PVI-6001A

Version : <u>0.4</u>

### Electrophoretic display controller SPECIFICATION

### MODEL NAME: PVI-6001A(P-TFBGA-177)

Customer's Confirmation

Customer

Date

By

PVI's Confirmation

Confirmed By

Prepared By

# PRIME VIEW INTERNATIONAL CO.,LTD.

3,LI SHIN RD. 1,SCIENCE-BASED INDUSTRIAL PARK,HSINCHU,TAIWAN,R.O.C.

http://www.pvi.com.tw

Date : JAN/08/2007

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 1 -

| 1. GEN         | IERAL DESCRIPTION                       |   |

|----------------|-----------------------------------------|---|

|                |                                         |   |

| 2. FEA         | TURES                                   | 4 |

| 3. QUI         | CK REFERENCE DATA                       |   |

| 4. BLO         | OCK DIAGRAM APOLLO                      |   |

| 5. PINI        | NING                                    |   |

| 6. ELE         | CTRICAL SPECIFICATIONS                  |   |

| 6.1            | ABSOLUTE MAXIMUM RATINGS                |   |

| 6.2            | RECOMMENDED OPERATING RANGE             |   |

|                | DC ELECTRICAL CHARACTERISTICS           |   |

| 6.4            | AC ELECTRICAL CHARACTERISTICS           |   |

| . TIM          | ING SPECIFICATION                       |   |

| 7.1            | SRAM MEMORY INTERFACE                   |   |

| 7.2            | FLASH ROM MEMORY INTERFACE              |   |

| 7.3            | TIMING HOST INTERFACE                   |   |

|                | T PROTOCOL                              |   |

|                | INECTION AND OVERVIEW.                  |   |

|                | NAL DESCRIPTION                         |   |

|                | H_DS                                    |   |

|                | H_RW<br>H_D[7:0]                        |   |

|                | H_D[7:0]                                |   |

|                | H ACK                                   |   |

|                | H <sup>-</sup> WUP                      |   |

| 8.2.7          | H_NRST                                  |   |

|                | D AND WRITE SEQUENCES                   |   |

|                | Write sequence                          |   |

|                | H_ACK and bus error<br>Read Precautions |   |

| 0.5.51         |                                         |   |

| ). POW         | VER MANAGEMENT FUNCTION                 |   |

| 9.1.1          |                                         |   |

| 9.1.2          |                                         |   |

| 9.1.3<br>9.1.4 |                                         |   |

| 9.1.4<br>9.1.5 |                                         |   |

| 0. C           | OMMAND DESCRIPTION                      |   |

| 10.1.00        | DMMAND LISTS                            |   |

|                | DMMAND DETAILS                          |   |

|                | 1 Load Picture (0xA0)                   |   |

| ·····          |                                         |   |

| 10.2.          | 2 Stop Loading (0xA1)                   |   |

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. -2-

| 10.2.4  | Erase Display (0xA3)           | 26   |

|---------|--------------------------------|------|

| 10.2.5  | Init Display (0xA4)            | 26   |

| 10.2.6  | Restore Picture (0xA5)         | 27   |

| 10.2.7  | Get Status (0xAA)              | 27   |

| 10.2.8  | Load Partial Picture (0xB0)    | . 27 |

| 10.2.9  | Display Partial Picture (0xB1) | . 28 |

| 10.2.10 | Version Number (0xE0)          | . 28 |

| 10.2.11 | Display Size (0xE2)            | . 28 |

| 10.2.12 | Reset (0xEE)                   | 29   |

| 10.2.13 | Normal Mode (0xF0)             | 29   |

| 10.2.14 | Sleep Mode (0xF1)              | .29  |

| 10.2.15 | Standby Mode (0xF2)            | . 29 |

| 10.2.16 | Set Depth (0xF3)               | . 29 |

| 10.2.17 | Orientation (0xF5)             | . 30 |

| 10.2.18 | Positive Picture (0xF7)        | . 30 |

| 10.2.19 | Negative Picture (0xF8)        | . 31 |

| 10.2.20 | Write to FLASH ROM (0x01)      | . 31 |

| 10.2.21 | Read from FLASH ROM (0x02)     | . 31 |

| 10.2.22 | Write Register (0x10)          | . 31 |

| 10.2.23 | Read Register (0x11)           | . 31 |

| 10.2.24 | Read Temperature (0x21)        | . 31 |

| 10.2.25 | Auto Refresh (0xF9)            | . 32 |

| 10.2.26 | Cancel Auto Refresh (0xFA)     | . 32 |

| 10.2.27 | Set Refresh Timer (0FB)        | . 32 |

| 10.2.28 | Manual Refresh (0xFC)          | 32   |

| 10.2.29 | Read Refresh Timer (0xFD)      | . 32 |

| 11.  | REGISTER DETAILS                                     |    |

|------|------------------------------------------------------|----|

| 11.1 | COMMON PWM                                           |    |

| 11.2 |                                                      |    |

| 11.3 | LOOK UP TABLE                                        |    |

| 11.4 | Grd H,                                               |    |

| 11.5 |                                                      |    |

| 11.6 |                                                      |    |

| 11.7 | I O WERTOONET                                        |    |

| 11.8 |                                                      |    |

| 11.9 | Temperature sensor                                   |    |

| 12.  | STATUS DETAIL                                        |    |

| 13.  | DATA FORMAT AND DISPLAY WAVEFORM                     |    |

| 13.1 | BINARY DISPLAY MODE                                  |    |

| 13.2 |                                                      |    |

| 13.3 | DISPLAY UPDATE OPERATIONS - MONOCHROME vs. GRAYSCALE |    |

| 14.  | THE DEFAULT VALUE AFTER RESET                        |    |

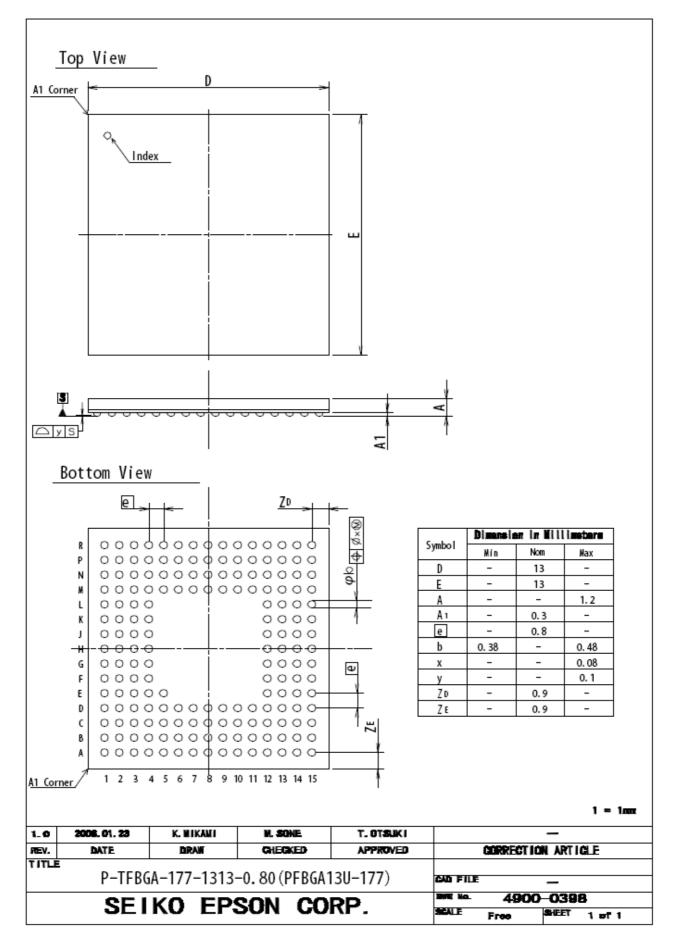

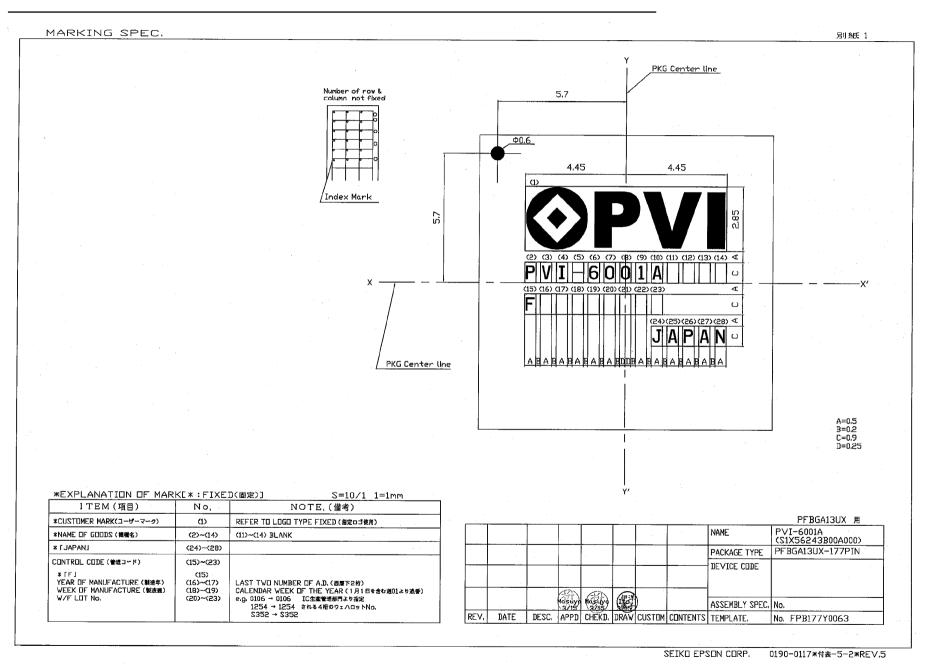

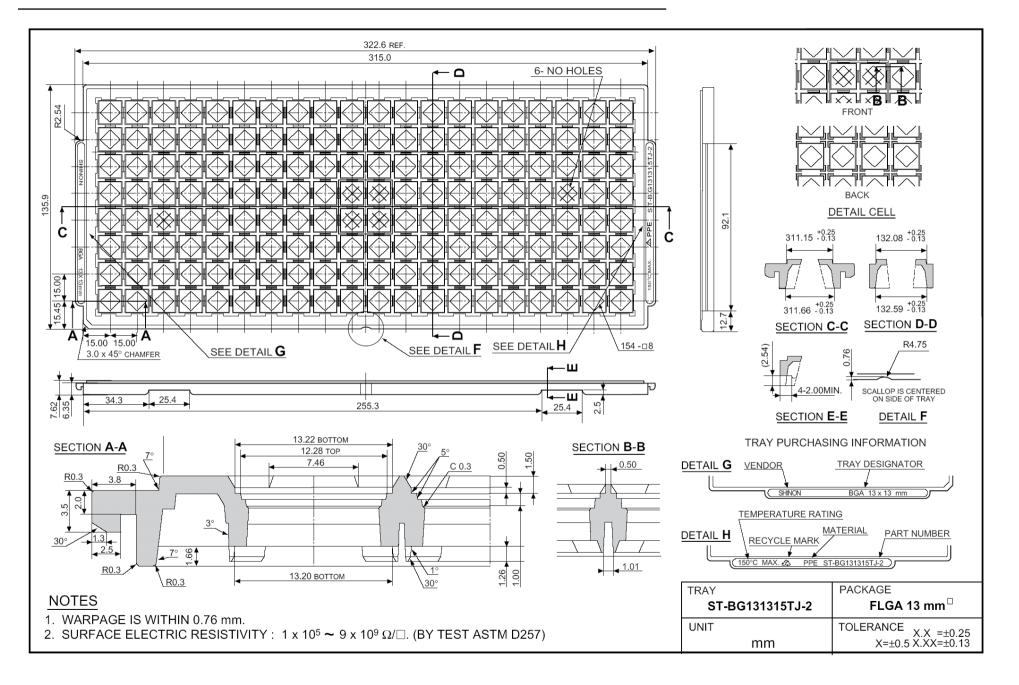

| APPE | NDIX A: PACKAGE INFORMATION                          | 40 |

| APPE | NDIX B: BLOCK DIAGRAM REFERENCE DESIGN               |    |

#### **1. GENERAL DESCRIPTION**

The PVI-6001A display controller is a display controller for a TFT (thin film transistor) active matrix Electrophoretic display. It is part of a reference system electronics design designed for Electrophoretic displays.

The PVI-6001A is suitable for 800 x 600 pixels, and has 1-bit and 2-bit display capabilities. It has an aspect ratio of 4:3, portrait or landscape. The PVI-6001A drives the source and gate drivers. It has an 8bit parallel asynchronous data bus and uses external SRAM memory to store the display data. It composes the required display waveforms to generate images on the displays using an external Look-Up-Table (flash memory).

The IC is designed for an electrophoretic display used with a reference system electronics design describing the necessary support electronics, and operating firmware defining key parameters of the display operation

This specification describes the performance and key electrical specification of the PVI-6001A display controller.

#### 2. FEATURES

- \* TFT electrophoretic display controller

- \* 800 x 600 pixels

- \* 4:3 aspect ratio, portrait or landscape.

- \* Uses two clock frequencies to reduce power. (33Mhz and 70 KHz)

- \* Two low power modes available. (Sleep and standby).

- \* Built-in buffer for rotation of orientation. (Portrait or landscape).

- \* Black and White or 4 levels grayscale mode.

- \* Capable of partial write operations in rectangular regions indicated by two apexes.

- \* Industrial temperature range.

- \*8- bit parallel bi-directional asynchronous interface, with handshake protocol.

- \* Maximum communication speed of host interface is 10 Mbytes/sec.

- \* One or more controllers can be connected to the host bus.

- \* Uses I2c master interface for temperature sensor.

- \* Uses double external low power SRAM (70 nsec access time).

- \* Uses external Flash Rom as Look-Up-Table (90 nsec access time).

- \* Available in a 177 pins lead free P-TFBGA package.

#### 3. QUICK REFERENCE DATA

| Electrophoretic display controller<br>(electronic ink display; E-Ink display)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVI-6001A<br>2.7 ~ 3.6 V<br>85 ~ -20 °C<br>CMOS 0.35um<br>: P-TFBGA-177 lead free<br>: 13 x 13 mm<br>0.8 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VSS B44<br>VSS CM4<br>VSS CJ12<br>VSS CJ12<br>VSS EJ4<br>VSS FG4<br>VSS FG4<br>VSS HE12<br>VSS HE12<br>VSS HD10<br>VSS ND7<br>VSS ND7<br>VSS ND7<br>VSS ND7<br>VSS PC15<br>VSS PC15<br>VSS PC15<br>VSS PC15<br>VSS PC14<br>VD0 0P11<br>VD0 | VDD 800<br>VDD 9613<br>VDD 9613<br>VDD 9613<br>VDD 9013<br>VDD 905<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 600<br>VDD 900<br>VDD 9000<br>VDD 900<br>VDD 900<br>VDD 900<br>VDD 900<br>VDD 900<br>VDD 900<br>VDD 900                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PVI-6001A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SRC_CL<br>SRC_CE<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_CE3<br>SRC_DE4<br>A13<br>SRC_D4<br>A13<br>SRC_D4<br>A13<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>A15<br>SRC_D2<br>SRC_D2<br>SI<br>SRC_D2<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_D2<br>SLC<br>SRC_SRC_D2<br>SLC<br>SRC_SRC_D2<br>SLC<br>SRC_SRC_D2<br>SLC<br>SRC_SRC_D2<br>SLC<br>SRC_SRC_D2<br>SLC<br>SRC_SRC_SRC_SRC_SRC_SRC_SRC_SRC_SRC_SRC_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R NUB2<br>R NOE<br>R NOE<br>R NME<br>R NME<br>H CC<br>H LC<br>H LC<br>H D1<br>H D1<br>H D2<br>H D3<br>H D4<br>H D5<br>H D5<br>H D5<br>H D5<br>H D7<br>H D7<br>H D7<br>H D7<br>H D7<br>H D7<br>H D7<br>H D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{c} \text{TST0} \\ \hline \text{F13} \\ \hline \text{F13} \\ \hline \text{F13} \\ \hline \text{F13} \\ \hline \text{F11} \\ \hline \text{F11} \\ \hline \text{F12} \\ \hline \text{TST2} \\ \hline \text{F12} \\ \hline \text{F12} \\ \hline \text{NC} \\ -1 \\ \hline \text{H12} \\ \hline \text{NC} \\ -2 \\ \hline \text{M11} \\ \hline \text{NC} \\ -5 \\ \hline \text{NC} \\ -5 \\ \hline \text{R2} \\ \hline \text{NC} \\ -7 \\ \hline \\ -2 \\ \hline -2 \\ \hline \\ -2 \\ \hline -2 \\ \hline \\ -2 \\ \hline \\ -2 \\ \hline -2 \\ \hline \\ -2 \\ \hline \\ -2 \\ \hline -2 \\ \hline -2 \\ \hline \\ -2 \\ \hline -2 \\ \hline \\ -2 \\ \hline -2 $ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (electronic ink display; E-Ink display)<br>PVI-6001A<br>2.7 ~ 3.6 V<br>85 ~ -20 °C<br>CMOS 0.35um<br>P-TFBGA-177 lead free<br>: 13 x 13 mm<br>0.8 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Figure 3.1 Symbol PVI-6001A

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. -5-

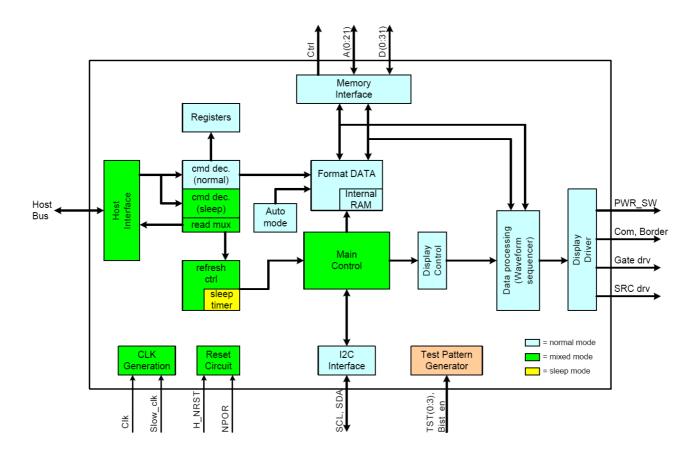

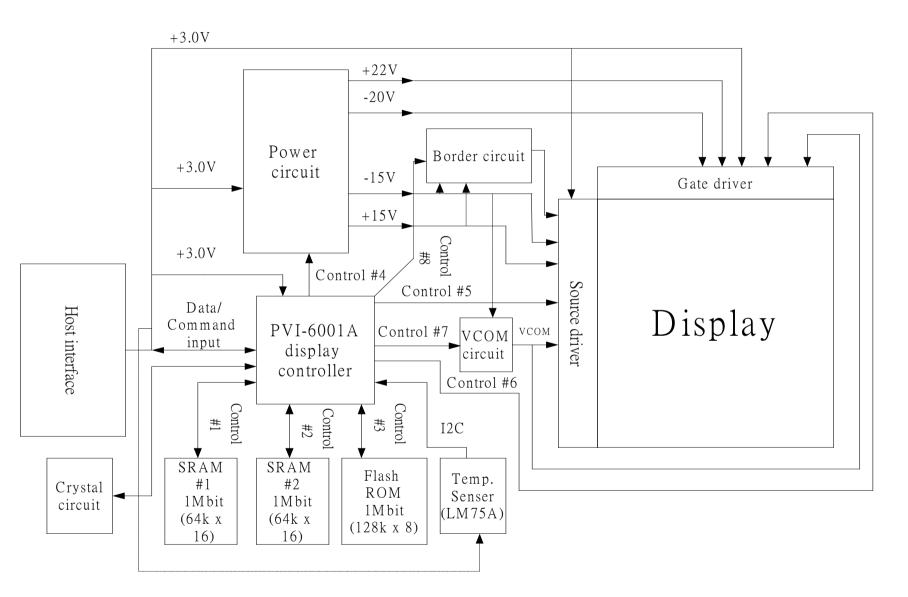

#### 4. BLOCK DIAGRAM PVI-6001A

Figure 4.1 Block diagram PVI-6001A

### 5. PINNING

| Name             | Pin number | Туре            | Description          |

|------------------|------------|-----------------|----------------------|

| Clock circuit    |            | :}              |                      |

| CLK              | N11        | Clock input     | Clock_input(+)       |

| CLK OUT          | N12        | Clock output    | Clock output(-)      |

| SLOW CLK IN      | R9         | In,COMS-schmitt | Slow_clock_input(+)  |

| SLOW_CLK_IN      | P9         | Output          | Slow clock middle    |

| SLOW_CLK_MID     | R10        |                 |                      |

| NPOR             | L13        | Output          | Slow_clock_output(-) |

| SRAM & Flash ROM |            | In,CMOS-schmitt | Power Up reset       |

|                  |            |                 | Data hua 22 hita     |

| D0               | N1         |                 | Data bus 32 bits     |

| D1               | R1         | I/O,CMOS        | Data bus 32 bits     |

| D2               | N3         | I/O,CMOS        | Data bus 32 bits     |

| D3               | R3         | I/O,CMOS        | Data bus 32 bits     |

| D4               | R4         | I/O,CMOS        | Data bus 32 bits     |

| D5               | R5         | I/O,CMOS        | Data bus 32 bits     |

| D6               | R6         | I/O,CMOS        | Data bus 32 bits     |

| D7               | R7         | I/O,CMOS        | Data bus 32 bits     |

| D8               | P2         | I/O,CMOS        | Data bus 32 bits     |

| D9               | P3         | I/O,CMOS        | Data bus 32 bits     |

| D10              | P4         | I/O,CMOS        | Data bus 32 bits     |

| D11              | P5         | I/O,CMOS        | Data bus 32 bits     |

| D12              | P6         | I/O,CMOS        | Data bus 32 bits     |

| D13              | P7         | I/O,CMOS        | Data bus 32 bits     |

| D14              | R8         | I/O,CMOS        | Data bus 32 bits     |

| D15              | P8         | I/O,CMOS        | Data bus 32 bits     |

| D16              | E3         | I/O,CMOS        | Data bus 32 bits     |

| D17              | A1         | I/O,CMOS        | Data bus 32 bits     |

| D18              | C6         | I/O,CMOS        | Data bus 32 bits     |

| D19              | A2         | I/O,CMOS        | Data bus 32 bits     |

| D20              | B3         | I/O,CMOS        | Data bus 32 bits     |

| D21              | A3         | I/O,CMOS        | Data bus 32 bits     |

| D22              | B4         | I/O,CMOS        | Data bus 32 bits     |

| D23              | A4         | I/O,CMOS        | Data bus 32 bits     |

| D24              | B5         | I/O,CMOS        | Data bus 32 bits     |

| D25              | A5         | I/O,CMOS        | Data bus 32 bits     |

| D26              | B6         | I/O,CMOS        | Data bus 32 bits     |

| D27              | A6         | I/O,CMOS        | Data bus 32 bits     |

| D28              | B7         | I/O,CMOS        | Data bus 32 bits     |

| D29              | A7         | I/O,CMOS        | Data bus 32 bits     |

| D30              | B8         | I/O,CMOS        | Data bus 32 bits     |

| D31              | A8         |                 | Data bus 32 bits     |

| A0               | C1         | Out,CMOS        | Address bus 22bits   |

| A0<br>A1         | C1<br>C2   | Out,CMOS        | Address bus 22bits   |

| A2               | <br>D1     | Out,CMOS        | Address bus 22bits   |

| A2<br>A3         | D1<br>D2   | Out,CMOS        | Address bus 22bits   |

|                  |            |                 |                      |

| A4               | E2         | Out,CMOS        | Address bus 22bits   |

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. -7-

| A5                   | E2  |                      | Address bus 22bits            |

|----------------------|-----|----------------------|-------------------------------|

| A6                   | F1  |                      |                               |

| A7                   | F2  | Out,CMOS             |                               |

| A8                   | G1  | Out,CMOS             | Address bus 22bits            |

| A9                   | G2  | Out,CMOS             | Address bus 22bits            |

| A10                  | G3  | Out,CMOS             | Address bus 22bits            |

| A11                  | H2  | Out,CMOS             | Address bus 22bits            |

| A12                  | H1  | Out,CMOS             | Address bus 22bits            |

| A13                  | J2  | Out,CMOS             | Address bus 22bits            |

| A14                  | J1  | Out,CMOS             | Address bus 22bits            |

| A15                  | K2  | Out,CMOS             | Address bus 22bits            |

| A16                  | K1  | Out,CMOS             | Address bus 22bits            |

| A17                  | L2  | Out,CMOS             | Address bus 22bits            |

| A18                  | J3  | Out,CMOS             |                               |

| A19                  | M2  | Out,CMOS             | Address bus 22bits            |

| A20                  | L1  | Out,CMOS             | Address bus 22bits            |

| A21                  | L3  | Out,CMOS             | Address bus 22bits            |

| F RDY                | M3  | In,CMOS              | Flash control ready not busy  |

| F_NCE                | D3  | Out,CMOS             | Flash control chip enable     |

| F NRST               | K3  | Out,CMOS             | Flash control nreset          |

| F NWE                | N6  | Out,CMOS             | Flash control write enable    |

| F NOE                | F3  |                      |                               |

| R NLB1               | C12 | Out,CMOS<br>Out,CMOS | Flash control output enable   |

|                      |     | •                    | SRAM control byte select 0    |

| R_NUB1               | C10 | Out,CMOS             | SRAM control byte select 1    |

| R_NLB2               | C7  | Out,CMOS             | SRAM control byte select 2    |

| R_NUB2               | C5  | Out,CMOS             | SRAM control byte select 3    |

| R_NCS                | B10 | Out,CMOS             | SRAM control chip select      |

| R_NOE                | B11 | Out,CMOS             | SRAM control output enable    |

| R_NWE                | B9  | Out,CMOS             | SRAM control write enable     |

| Display Source Drive |     |                      |                               |

| SRC_D0               | C13 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D1               | A15 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D2               | C11 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D3               | A13 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D4               | A12 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D5               | A11 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D6               | A10 | Out,CMOS             | Source driver data bus(8bits) |

| SRC_D7               | A9  | Out,CMOS             | Source driver data bus(8bits) |

| SRC_CE1              | B14 | Out,CMOS             | Source driver chip enable 1   |

| SRC_CE2              | B13 | Out,CMOS             | Source driver chip enable 2   |

| SRC_CE3              | B12 | Out,CMOS             | Source driver chip enable 3   |

| SRC_OE               | D14 | Out,CMOS             | Source driver output enable   |

| SRC_LE               | C14 | Out,CMOS             | Source driver latch enable    |

| SRC_CL               | E13 | Out,CMOS             | Source driver Clock           |

| Display Gate Driver  |     |                      |                               |

| GT_CKV               | E15 | Out,CMOS             | Gate driver clock             |

| GT_SPV               | D15 | Out,CMOS             | Gate driver start pulse       |

| GT_CASC              | F14 | Out,CMOS             | Gate driver cascade select    |

| GT MODE              | E14 | Out,CMOS             | Gate driver mode select       |

|                      | 1   | _ ·, = · · · • •     |                               |

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. -8-

| <b>Display Control Sign</b> | nals |                    |                                 |

|-----------------------------|------|--------------------|---------------------------------|

| BORDER0                     | M13  | Out,CMOS           | Display border control signal   |

| BORDER1                     | R15  | Out,CMOS           | Display border control signal   |

| PWR_POS                     | P13  | Out,CMOS           | Positive voltage supply on      |

| PWR_NEG                     | N14  | Out,CMOS           | Negative voltage supply on      |

| PWR_GATE                    | P14  | Out,CMOS           | Gate voltage on                 |

| COM_PWM                     | R13  | Out,CMOS           | Display common pwm out          |

| COM_CTRL                    | N13  | Out,CMOS           | Display common switch           |

| Host Interface              |      |                    |                                 |

| H_CD                        | G14  | In LVTTL,schmitt   | Host interface Command/not data |

| H_DS                        | M15  | In LVTTL,schmitt   | Host interface device select    |

| H_NRST                      | F15  | In LVTTL,schmitt   | Host interface reset low active |

| H_RW                        | N15  | In LVTTL,schmitt   | Host interface read/not write   |

| H_WUP                       | G15  | In LVTTL,schmitt   | Host interface wake up          |

| H_ACK                       | M14  | Tri-state out CMOS | Host interface acknowledge      |

| H_D0                        | L15  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D1                        | L14  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D2                        | K15  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D3                        | K14  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D4                        | J15  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D5                        | J14  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D6                        | H15  | I/O LVTTL          | Host interface data bus(8bits)  |

| H_D7                        | H14  | I/O LVTTL          | Host interface data bus(8bits)  |

| 12C                         |      |                    |                                 |

| SCL                         | R12  | I/O LVTTL Schmitt  | I2C clock                       |

| SDA                         | P12  | I/O LVTTL Schmitt  | I2C data                        |

| Others                      |      |                    |                                 |

| TST0                        | F13  | In CMOS            | Select test mode(normal='0')    |

| TST1                        | P10  | In CMOS            | Select test mode(normal='0')    |

| TST2                        | K13  | In CMOS            | Select test mode(normal='0')    |

| TST3                        | J13  | In CMOS            | Select auto mode(normal='0')    |

| BIST_EN                     | N5   | In CMOS            | Chip memory mode(normal='0')    |

| Not connected               |      |                    |                                 |

| n.c.                        | A14  |                    | Not connected                   |

| n.c.                        | B1   |                    | Not connected                   |

| n.c.                        | B15  |                    | Not connected                   |

| n.c.                        | C9   |                    | Not connected                   |

| n.c.                        | D8   |                    | Not connected                   |

| n.c.                        | E5   |                    | Not connected                   |

| n.c.                        | F12  |                    | Not connected                   |

| n.c.                        | H4   |                    | Not connected                   |

| n.c.                        | H12  |                    | Not connected                   |

| n.c.                        | M8   |                    | Not connected                   |

| n.c.                        | M11  |                    | Not connected                   |

| n.c.                        | N7   |                    | Not connected                   |

| n.c.                        | R2   |                    | Not connected                   |

| n.c.                        | R14  |                    | Not connected                   |

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 9 -

| Power pins |       |       |

|------------|-------|-------|

| VDD        | C3    | +3.0V |

| VDD        | C8    | +3.0V |

| VDD        | D4    | +3.0V |

| VDD        | D5    | +3.0V |

| VDD        | D11   | +3.0V |

| VDD        | D13   | +3.0V |

| VDD        | G13   | +3.0V |

| VDD        | H3    | +3.0V |

| VDD        | H13   | +3.0V |

| VDD        | L4    | +3.0V |

| VDD        | M1    | +3.0V |

| VDD        | M4    | +3.0V |

| VDD        | M7    | +3.0V |

| VDD        | M12   | +3.0V |

| VDD        | N4    | +3.0V |

| VDD        | N9    | +3.0V |

| VDD        | P11   | +3.0V |

| GND        | · · · |       |

| VSS        | B2    | GND   |

| VSS        | C4    | GND   |

| VSS        | C15   | GND   |

| VSS        | D6    | GND   |

| VSS        | D7    | GND   |

| VSS        | D9    | GND   |

| VSS        | D10   | GND   |

| VSS        | D12   | GND   |

| VSS        | E4    | GND   |

| VSS        | E12   | GND   |

| VSS        | F4    | GND   |

| VSS        | G4    | GND   |

| VSS        | G12   | GND   |

| VSS        | J4    | GND   |

| VSS        | J12   | GND   |

| VSS        | K4    | GND   |

| VSS        | K12   | GND   |

| VSS        | L12   | GND   |

| VSS        | M5    | GND   |

| VSS        | M6    | GND   |

| VSS        | M9    | GND   |

| VSS        | M10   | GND   |

| VSS        | N2    | GND   |

| VSS        | N8    | GND   |

| VSS        | N10   | GND   |

| VSS        | P1    | GND   |

| VSS        | P15   | GND   |

| VSS        | R11   | GND   |

Table 5.1 Pinning

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 10 -

#### 6. ELECTRICAL SPECIFICATIONS

#### 6.1 Absolute maximum ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.

| Symbol           | Parameter                  | Conditions          | Min   | Тур | Max     | Unit |  |  |  |

|------------------|----------------------------|---------------------|-------|-----|---------|------|--|--|--|

| Supply Voltage   | Supply Voltage             |                     |       |     |         |      |  |  |  |

| V <sub>DD</sub>  | DC Supply voltage          | V <sub>SS</sub> =0V | -0.3V |     | +5.0    | V    |  |  |  |

| Pin Voltage      |                            |                     |       |     |         |      |  |  |  |

| V <sub>IN</sub>  | DC Input voltage           | V <sub>SS</sub> =0V | -0.3  |     | VDD+0.3 | V    |  |  |  |

| V <sub>OUT</sub> | DC Output voltage          | V <sub>SS</sub> =0V | -0.3  |     | VDD+0.3 | V    |  |  |  |

| DC input curre   | ent(max current input pin) |                     |       |     |         |      |  |  |  |

| l <sub>in</sub>  | DC input current           | V <sub>SS</sub> =0V | -10   |     | +10     | mA   |  |  |  |

| Temperature      |                            |                     |       |     |         |      |  |  |  |

| T <sub>STG</sub> | Storage temperature        |                     | -40   |     | +125    | °C   |  |  |  |

Table 6.1 Absolute maximum ratings

#### 6.2 Recommended operating range

| Symbol           | Parameter             | Conditions          | Min  | Тур   | Max             | Unit |

|------------------|-----------------------|---------------------|------|-------|-----------------|------|

| Supply voltage   | •                     | •                   | •    | • • • |                 |      |

| V <sub>DD</sub>  | DC Supply voltage     | V <sub>SS</sub> =0V | 2.7  | 3.0   | 3.6             | V    |

| DC input voltage | e                     |                     |      |       |                 |      |

| V <sub>IN</sub>  | DC input voltage      | V <sub>SS</sub> =0V | 0    |       | V <sub>DD</sub> | V    |

| Temperature      |                       |                     |      |       |                 |      |

| TJ               | Junction temperature  |                     | -5   |       | 100             | °C   |

| Tamb             | Ambient temperature   |                     | -20  |       | 85              | °C   |

| Clock frequency  | /                     |                     |      |       |                 | -    |

| FCLK             | Clock frequency       |                     | 32.5 | 33    | 33.5            | Mhz  |

| FSLOWCLK         | Slow clock frequency  |                     | 60   | 70    | 80              | Khz  |

| DCLK             | Duty cycle clock      |                     | 40   | 50    | 60              | %    |

| DSLOWCLK         | Duty cycle slow clock |                     | 20   | 50    | 80              | %    |

Table 6.2 Recommended operating range

#### 6.3 DC Electrical Characteristics

| Symbol             | Parameter                   | Conditions            | Min | Тур | Max | Unit |

|--------------------|-----------------------------|-----------------------|-----|-----|-----|------|

| Supply Current     |                             |                       |     |     |     |      |

| I <sub>DD</sub>    | Normal mode supply current  | V <sub>DD</sub> =3.0V |     | 40  | 50  | mA   |

| I <sub>SLEEP</sub> | Sleep mode supply current   | V <sub>DD</sub> =3.0V |     | 400 | 600 | μA   |

| ISTANDBY           | Standby mode supply current | V <sub>DD</sub> =3.0V |     | 0.1 | 1   | μA   |

| Symbol          | Parameter                          | Conditions                                   | Min                   | Тур | Max                   | Unit    |

|-----------------|------------------------------------|----------------------------------------------|-----------------------|-----|-----------------------|---------|

| Input voltage   |                                    | -                                            | <u>.</u>              |     | · · ·                 |         |

|                 | High level input voltage           |                                              |                       |     |                       |         |

|                 | LVTTL                              |                                              | 2.0                   |     |                       | V       |

| VIH             | LVTTL Schmitt-trigger              |                                              | 2.0                   |     |                       | V       |

|                 | CMOS                               |                                              | 0.8V <sub>DD</sub>    |     |                       | V       |

|                 | CMOS Schmitt-trigger               |                                              | $0.8V_{DD}$           |     |                       | V       |

|                 | Low level input current            |                                              |                       |     |                       | V       |

|                 | LVTTL                              |                                              |                       |     | 0.8                   | V       |

| VIL             | LVTTL Schmitt-trigger              |                                              |                       |     | 0.8                   | V       |

|                 | CMOS                               |                                              |                       |     | 0.2 V <sub>DD</sub>   | V       |

|                 | CMOS Schmitt-trigger               |                                              |                       |     | 0.2 V <sub>DD</sub>   | V       |

| I <sub>IH</sub> | High level input current           | V <sub>IN</sub> =V <sub>DD</sub>             | -10                   |     | 10                    | $\mu$ A |

| I <sub>IL</sub> | Low level input current            | V <sub>IN</sub> =V <sub>SS</sub>             | -10                   |     | 10                    | $\mu$ A |

| I <sub>OZ</sub> | High impedance leakage current     | Vout = V <sub>DD</sub><br>or V <sub>SS</sub> | -10                   |     | 10                    | μA      |

| V <sub>H</sub>  | Schmitt-trigger hysteresis voltage |                                              |                       |     |                       |         |

|                 | LVTTL                              |                                              |                       | 0.5 |                       | V       |

|                 | LVTTL Schmitt-trigger              |                                              |                       | 0.5 |                       | V       |

| Output voltage  |                                    |                                              |                       |     |                       |         |

| V <sub>OH</sub> | High level output voltage          | $I_{OH} = -4mA$                              | 2.4                   |     |                       |         |

|                 |                                    | I <sub>OH</sub> = -1 μ A                     | V <sub>DD</sub> -0.05 |     |                       |         |

| V <sub>OL</sub> | Low level output voltage           | I <sub>ОН</sub> = 4mA                        |                       |     | 0.4                   | V       |

|                 |                                    | I <sub>он</sub> = 1 <i>µ</i> А               |                       |     | V <sub>SS</sub> +0.05 | V       |

Table 6.3 DC characteristics

#### 6.4 AC Electrical Characteristics

| Symbol            | Parameter | Conditions | Min | Тур | Max | Unit |

|-------------------|-----------|------------|-----|-----|-----|------|

| Input capacitance | 9         |            |     |     |     |      |

| CINPUT            |           |            |     |     | 10  | pF   |

| Symbol             | Parameter                 | Conditions | Min | Тур | Max | Unit |

|--------------------|---------------------------|------------|-----|-----|-----|------|

| Reset(NPOR)        |                           |            |     |     |     |      |

| t <sub>reset</sub> | Minimum length NPOR reset |            | 40  |     |     | ns   |

| Symbo                 | I Parameter          | Conditions             | Min | Тур | Max | Unit |

|-----------------------|----------------------|------------------------|-----|-----|-----|------|

| SRAM & Fla            | ash interface        |                        |     |     |     |      |

| t <sub>rise mem</sub> | Rise time memory I/O | C <sub>pin</sub> =15pF |     | 3.3 |     | nsec |

| t <sub>fall mem</sub> | Fall time memory I/O | C <sub>pin</sub> =15pF |     | 3.4 |     | nsec |

Note: See also timing memory interface

| Symbol                | Parameter                 | Conditions             | Min  | Тур  | Max | Unit      |

|-----------------------|---------------------------|------------------------|------|------|-----|-----------|

| Display(Source,       | gate and control)         |                        |      |      |     |           |

| t <sub>rdisplay</sub> | Rise time display outputs | C <sub>pin</sub> =15pF |      | 3.3  |     | nsec      |

| t <sub>fdisplay</sub> | Fall time display outputs | C <sub>pin</sub> =15pF |      | 3.4  |     | nsec      |

| t <sub>spv</sub>      | Length GT_SPV pulse(low)  |                        |      | 60   |     | $\mu$ sec |

| t <sub>ckv</sub>      | Period GT_CKV pulse       |                        | 10.2 | 33   | 89  | $\mu$ sec |

| f <sub>cl</sub>       | Frequency SRC_CL pulse    |                        |      | 16.7 |     | MHz       |

| t <sub>le</sub>       | Length SRC_LE pulse       |                        |      | 30   |     | nsec      |

| D <sub>PWM</sub>      | Duty cycle pwm output     |                        | 0    |      | 100 | %         |

| Symbol                 | Parameter          | Conditions             | Min | Тур | Max | Unit |

|------------------------|--------------------|------------------------|-----|-----|-----|------|

| Host bus               |                    |                        |     |     |     |      |

| t <sub>rise host</sub> | Rise time host bus | C <sub>pin</sub> =15pF |     | 3.3 |     | nsec |

| t <sub>fall host</sub> | Fall time host bus | C <sub>pin</sub> =15pF |     | 3.4 |     | nsec |

Note: See also timing host bus interface

| Symbol             | Parameter             | Conditions             | Min | Тур  | Max | Unit |

|--------------------|-----------------------|------------------------|-----|------|-----|------|

| I2C                |                       |                        |     |      |     |      |

| f <sub>SCL</sub>   | Clock frequency       |                        |     | 400  |     | nsec |

| f <sub>fl2C</sub>  | Fall time I2C outputs | C <sub>pin</sub> =15pF |     | 2    |     | nsec |

| t <sub>ri2c</sub>  | Rise time I2C outputs |                        |     | N.A. |     |      |

| I <sub>inI2C</sub> | Maximum input current |                        |     |      | 4   | mA   |

Table 6.4 AC characteristics

\* Depends on bus load and external pull up resistor

#### 7. TIMING SPECIFICATION.

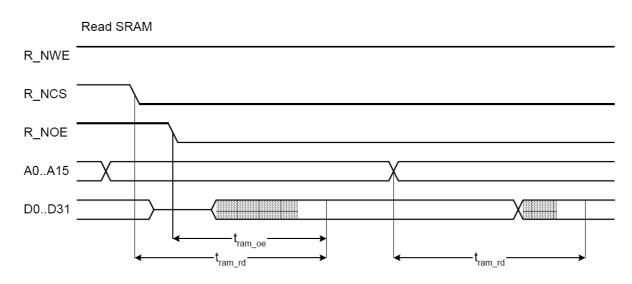

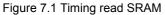

#### 7.1 SRAM memory interface

The SRAM memory interface uses a 32 x 64kbit memory interface. Although the address bus is 22 bits wide, only the lower 16 address bits (A0..A15) are used for the SRAM.

| Symbol              | Parameter                         | Min | Тур | Max | Unit |

|---------------------|-----------------------------------|-----|-----|-----|------|

| f <sub>ram_rd</sub> | Access time read for valid output | 75  |     |     | nsec |

| f <sub>ram oe</sub> | Output enable to valid output     | 45  |     |     | nsec |

| f <sub>ram wr</sub> | Access time write                 | 85  |     |     | nsec |

| f <sub>ram we</sub> | Write pulse width                 | 55  |     |     | nsec |

| f <sub>ram su</sub> | Setup up time data and address    | 0   |     |     | nsec |

| f <sub>ram ho</sub> | Hold time data and address        |     |     | 30  | nsec |

Table 7.1 Timing SRAM

Note: SRAM interface is designed for low power SRAM memories(70 nsec access time).

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 14 -

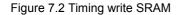

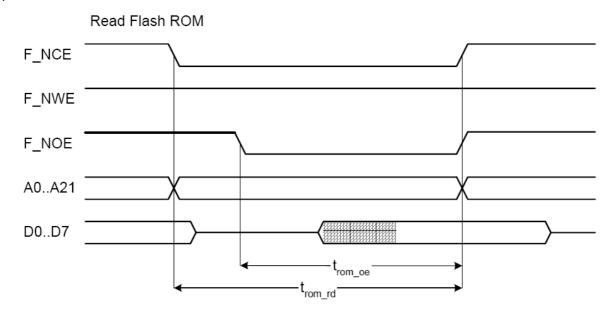

#### 7.2 FLASH ROM memory interface.

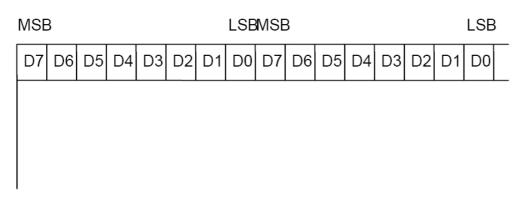

The FLASH ROM memory interface uses an 8 x 4Mbit memory interface. Although the data bus is 32 bits wide, only the lower 8 data bits (D0..D7) are used for the FLASH ROM. The memory interface is maximum 22 bits wide but can also be used with smaller devices. Minimum required size is 8x 64kBit.

Figure 7.3 Timing read Flash ROM

| Figure | 74  | Timing   | writa | Flach  | ROM |

|--------|-----|----------|-------|--------|-----|

| Figure | 1.4 | TITITITY | wille | FIASII | ROW |

| Symbol              | Parameter                         | Min | Тур | Max | Unit |

|---------------------|-----------------------------------|-----|-----|-----|------|

| f <sub>rom rd</sub> | Access time read for valid output | 100 |     |     | nsec |

| f <sub>rom oe</sub> | Output enable to valid output     | 70  |     |     | nsec |

| f <sub>rom wr</sub> | Access time write                 | 115 |     |     | nsec |

| f <sub>rom_we</sub> | Nominal access time write         | 85  |     |     | nsec |

| f <sub>rom su</sub> | Set up time for data write        | 0   |     |     | nsec |

| f <sub>rom_ho</sub> | Hold time data of data write      |     |     | 30  | nsec |

Table 7.2 Timing Flash ROM

Note: FLASH interface is designed for low voltage Flash memories (90 nsec access time)

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 15 -

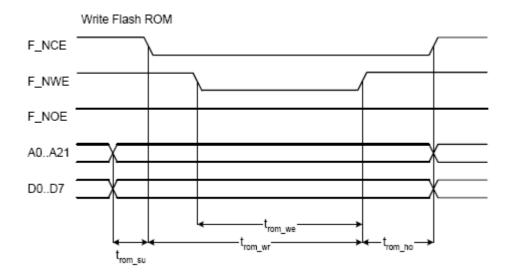

#### 7.3 Timing host interface

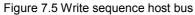

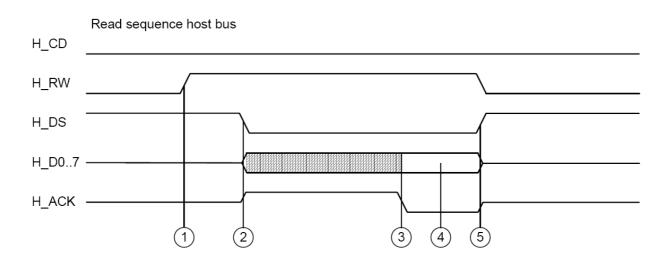

Figure 7.6 Read sequence host bus

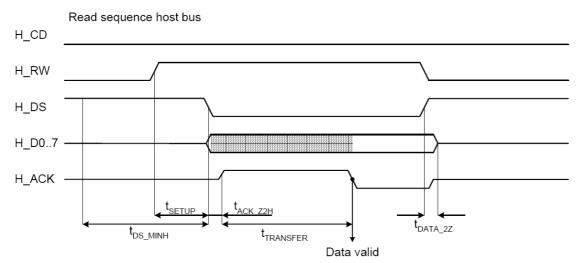

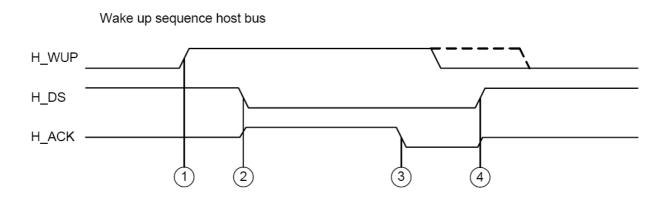

| Figure 7.7  | Wake up   | sequence  | host bus  |

|-------------|-----------|-----------|-----------|

| 1 19010 1.1 | rrance ap | 009401100 | 11001 040 |

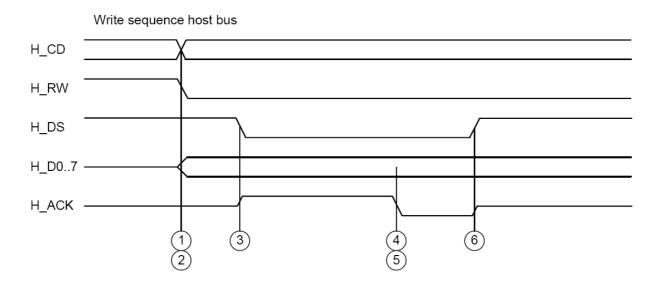

| Symbol                | Parameter                            | Min | Тур | Max             | Unit |

|-----------------------|--------------------------------------|-----|-----|-----------------|------|

| t <sub>DS MINH</sub>  | Minimum time high H_DS               | 35  |     |                 | nsec |

| t <sub>TRANSFER</sub> | Transfer time data                   | 60  | 75  |                 | nsec |

| t <sub>SETUP</sub>    | Setup time host bus                  | 20  |     |                 | nsec |

| t <sub>ACK Z2H</sub>  | Minimum response time of acknowledge |     |     | 10 <sup>*</sup> | nsec |

| t <sub>HOLD</sub>     | Hold time host bus                   | 0   |     |                 | nsec |

| t <sub>DATA 2Z</sub>  | Minimum release time of data bus     |     |     | 10              | nsec |

| t <sub>wup hl</sub>   | Minimum hold time WUP during wake-up | 35  |     |                 | nsec |

Table 7.3 Timing host bus

\* Response time is load dependent.(15pF).

It's recommended to use pull up resistor of 100K to ensure a normal high position.

The information contained herein is the exclusive property of Prime View International Co., Ltd. and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Prime View International Co., Ltd. - 17 -

#### 8. HOST PROTOCOL

This chapter covers the specifications of the host interface.

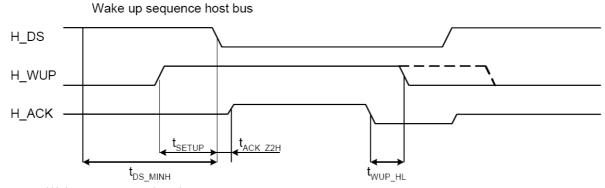

#### 8.1 Connection and overview.

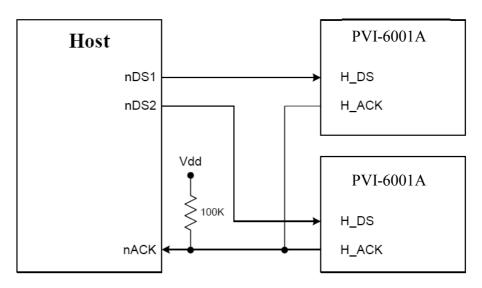

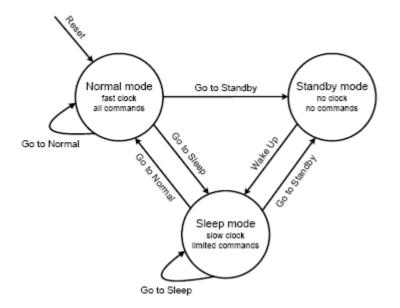

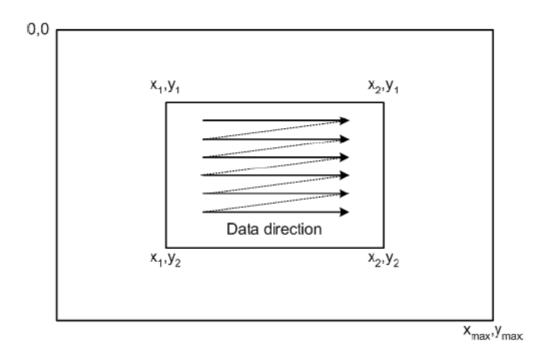

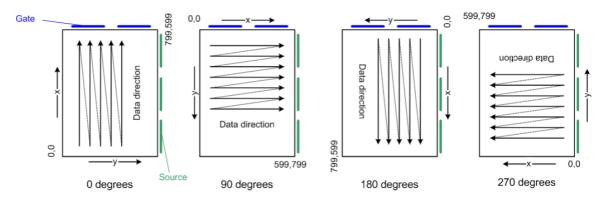

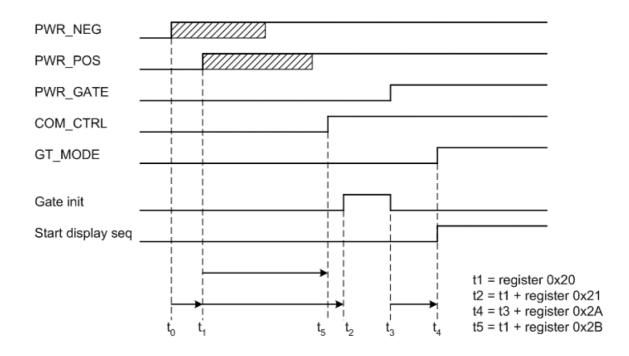

The controller is connected to the host via an 8-bit parallel interface. The interface transfer speed is max 10 MBytes/sec. The host communication protocol is an asynchronous interface with handshake. The host bus is designed to support multiple controllers connected to a single host bus.