**Integrated Mixed-Signal Solutions**

## PRODUCT DATA SHEET

# STMP35xx

D-Major™Audio System on Chip with USB 2.0, LCD, Voice Record and Battery Charger

> Third Generation Audio Decoder Version 1.03 September 17, 2003

### PRELIMINARY INFORMATION 9/17/03

#### 5-35xx-D1-1.03-091703

Copyright © 2003 SigmaTel, Inc. All rights reserved.

All contents of this document are protected by copyright law and may not be reproduced without the express written consent of SigmaTeI, Inc.

SigmaTel, the SigmaTel logo, and combinations thereof are registered trademarks and D-Major and C-Major are trademarks of SigmaTel, Inc. Other product names used in this publication are for identification purposes only and may be trademarks or registered trademarks of their respective companies. The contents of this document are provided in connection with SigmaTel, Inc. products. SigmaTel, Inc. has made best efforts to ensure that the information contained herein is accurate and reliable. However, SigmaTel, Inc. makes no warranties, express or implied, as to the accuracy or completeness of the contents of this publication and is providing this publication "AS IS". SigmaTel, Inc. reserves the right to make changes to specifications and product descriptions at any time without notice, and to discontinue or make changes to its products at any time without notice. This product is not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Any use or distribution of these products for uses in such applications do so at their own risk and agree to fully indemnify SigmaTel, Inc for any damages resulting from such applications. SigmaTel, Inc. does not assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential, or incidental damages.

# D-Major™Audio System on Chip

## 1. TABLE OF CONTENTS

| 1. TABLE OF CONTENTS                                       | 2   |

|------------------------------------------------------------|-----|

| 2. PRODUCT OVERVIEW                                        |     |

| 3. CHARACTERISTICS/SPECIFICATIONS                          | 21  |

| 4. DSP CORE                                                | 25  |

| 5. ON-CHIP MEMORY SUBSYSTEM                                | 31  |

| 6. CHIP WIDE PROGRAMMABLE CONTROL REGISTERS                | 39  |

| 7. INTERRUPT SUBSYSTEM                                     | 50  |

| 8. USB CONTROLLER                                          | 61  |

| 9. INTEGRATED USB 2.0 PHY (HS,FS)                          |     |

| 10. PARALLEL EXTERNAL MEMORY CONTROLLER (EMC)              | 102 |

| 11. GENERAL PURPOSE FLASH CONTROLLER                       | 116 |

| 12. FLASH ECC ACCELERATOR                                  |     |

| 13. FILTER COPROCESSOR (FILCO)                             |     |

| 14. PULSE WIDTH MODULATOR (PWM) CONTROLLER                 |     |

| 15. I <sup>2</sup> C INTERFACE                             | 193 |

| 16. ENHANCED SPI INTERFACE                                 | 204 |

| 17. SPI INTERFACE                                          |     |

| 18. TIMERS                                                 |     |

| 19. SDRAM INTERFACE                                        | 222 |

| 20. SWIZZLE                                                |     |

| 21. REAL-TIME CLOCK/ALARM/WATCHDOG RESET & PERSISTENT BITS |     |

| 22. I <sup>2</sup> S SERIAL AUDIO INTERFACE                |     |

| 23. GENERAL PURPOSE INPUT/OUTPUT (GPIO)                    |     |

| 24. DAC                                                    |     |

| 25. ADC                                                    | 279 |

| 26. MIXER                                                  |     |

| 27. HEADPHONE DRIVER                                       |     |

| 28. LOW RESOLUTION ADC                                     |     |

| 29. BOOT MODES                                             | _   |

| 30. DC-DC CONVERTER                                        |     |

| 31. PIN DESCRIPTION                                        |     |

| 32. PACKAGE DRAWINGS                                       | 380 |

| 33. INDEX OF REGISTERS                                     | 382 |

# **ADDITIONAL SUPPORT**

Additional product and company information can be obtained by going to the Sigma-Tel website at: <a href="https://www.sigmatel.com">www.sigmatel.com</a>. Additional product and design information is available for authorized customers at: <a href="https://extranet.sigmatel.com">extranet.sigmatel.com</a>

# D-Major™Audio System on Chip

#### 2. PRODUCT OVERVIEW

### 2.1. Features

- Decodes MP3 and WMA and is upgradeable to other digital music formats

- · Supports WMA Digital Rights Management (DRM) and other security schemes

- Includes on-chip read only unique ID for digital rights management algorithms

- USB High Speed Device Interface (up to 480Mb/s transfers)

- Enables file transfer and firmware upgrade using USB Mass Storage Class

- · Both Windows and Macintosh drivers available

- Integrated USB High Speed PHY

- Direct connection to USB 5V power for operation and battery charging

- 96K Words (288K Bytes) of on-chip RAM

- Hardware support for flexible external storage options

- NAND Flash, MMC, Secure Digital, SmartMedia, CompactFlash

- Five byte address support for new 1Gb/die (128KB block) NAND Flash

- · MLC NAND Flash support

- 1.8V NAND Interface Support

- 16 bit wide NAND support

- Hardware accelerated ECC offloads DSP bit error correction

- SDRAM

- ATA/IDE Hard Disk digital devices.

- · Optimized for very long battery life

- 50 hours of operation on a single AA battery

- Flexible, efficient on-chip DC-DC converter

- Flexible battery configurations, including 1xAA, 1xAAA, 2xAA, 2xAAA, Lilon

- · Pulse frequency modulation mode for low standby power

- Energy saving dynamic power management

- Typical off current is 250µA (crystal oscillator & real time clock only)

- More than 1 year battery life in "off" mode on one AA Alkaline battery

- Integrated battery charger for Lilon and NiMH

- Battery temperature sensor support for safest charging protocols

- Real time clock with alarm function wakes up from powerdown/standby modes

- High quality integrated audio mixed signal sub-system

- <0.05% THD direct drive headphone amplifier</li>

- Eliminates DC blocking capacitors

- Including anti-pop and short-circuit protection

- High performance 18-bit ΣΔ technology stereo D/A and A/D converters

- Full analog mixer configuration

- Line-in to Headphone/Line-out SNR >90 dB

- Two analog line-level inputs: Line1 In (stereo), Line2 In (stereo, 144-pin package)

- Mic(mono) input with integrated pre-amp and microphone biasing circuit

- Volume control

- GPIO, button I/O controls, and LCD/LED Display Compatible Interface

- · Pulse Width Modulators for EL backlights

- Integrated 75MHz DSP with Filter Coprocessor for power optimization

- Optimized for audio applications

- · Field upgradeable firmware

# D-Major™Audio System on Chip

- Integrated Development Environment, SDK, and debugger

- · Application and support libraries

- Bass and Treble control; configurable multiple band EQ control

- Voice record in ADPCM format (upgradable to other formats)

- · FM tuner input and control support

- Optional interface to a host chip/processor for cell phone & PDA applications, etc.

- Application notes, reference schematics, sample PCB layouts are available.

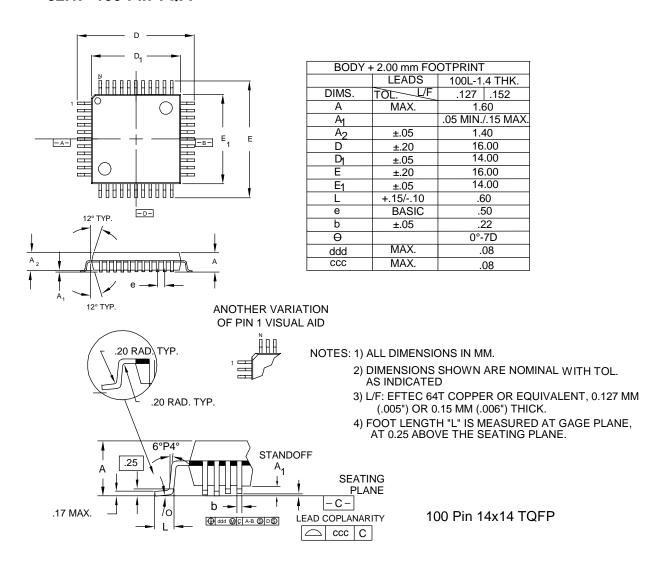

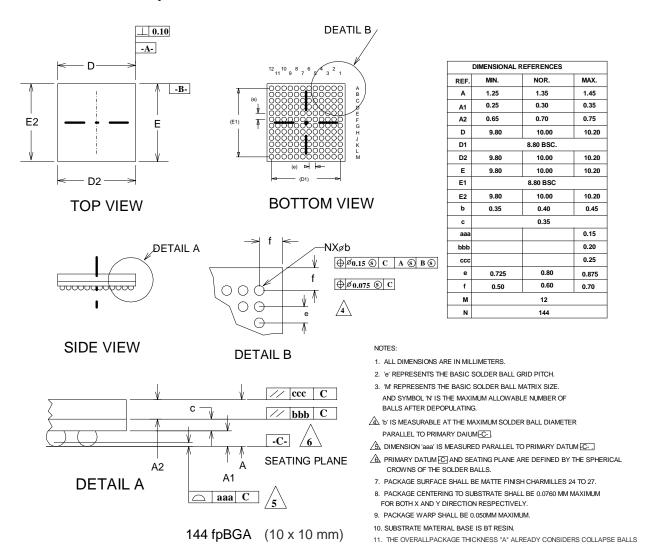

- Offered in 100-pin TQFP, and 144-pin fpBGA packages

- Backward pin and firmware compatible with STMP3410

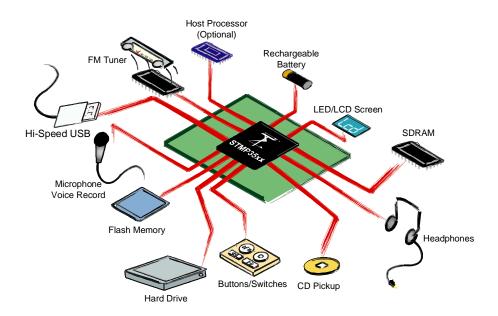

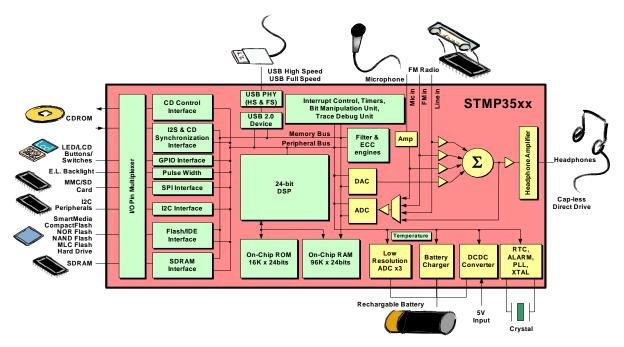

# 2.2. STMP35xx Block Diagram

Figure 1. Chip Block Diagram

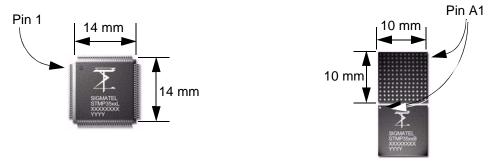

100-pin TQFP 144-pin fpBGA For additional package measurements, please see 32. "PACKAGE DRAWINGS" on page 380.

Figure 2. Chip Package Photos

# D-Major™Audio System on Chip

## 2.3. Description

SigmaTel's STMP35xx is a third generation single-chip highly-integrated digital music system solution for devices such as digital audio players, PDAs, voice recorders, MP3-encode recorders, and cell phones. It includes a high performance DSP, 288KBytes of on-chip SRAM, and a USB 2.0 interface (including High speed 480Mb/second transfers) for downloading music and uploading voice and MP3 recordings. The chip also includes a mixer, DAC, ADC and provides interfaces to IDE Hard Drives, CD-DSPs, Flash memory, LCD/LEDs, button & switch inputs, headphone driver, FM tuner input & controls and a microphone. The chip's highly programmable architecture supports MP3, WMA, and other digital audio standards. WMA digital rights management and other security schemes are also supported. For devices like PDAs and cell phones, the STMP35xx can act as a slave chip to a host chip/processor.

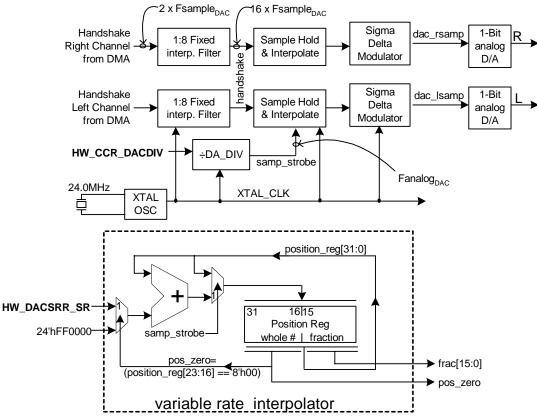

The DAC includes a headphone driver to directly drive low impedance headphones. The ADC includes inputs for both microphone and analog audio in to support voice recording & FM radio integration and MP3 encode features. SigmaTel's proprietary Sigma-Delta ( $\Sigma\Delta$ ) technology achieves a DAC SNR in excess of 90 dB for high-quality audio playback.

The STMP35xx has low power consumption to allow long battery life and includes an efficient flexible on-chip DC-DC converter that allows many different battery configurations, including 1xAA, 1xAAA, 2xAA, 2xAAA and Lilon. The chip includes an integrated intelligent charger for NiMH and Lilon batteries. In addition, the single-chip design and low pin count enables very small digital audio devices to be designed.

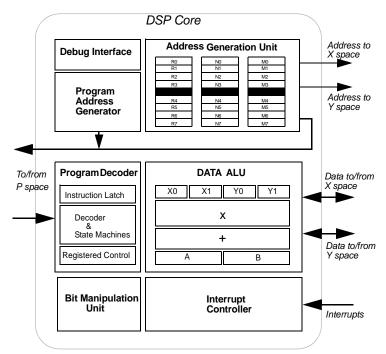

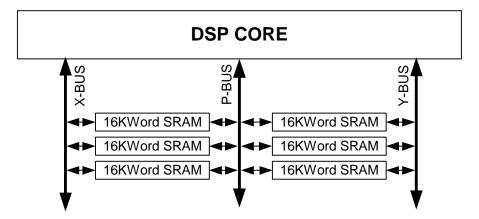

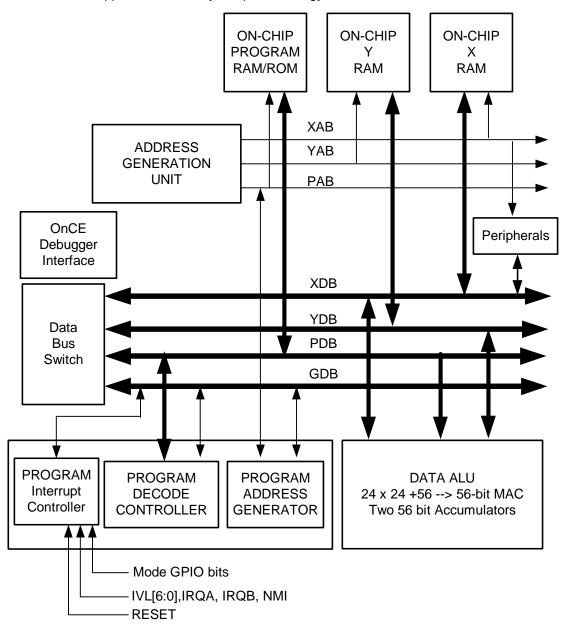

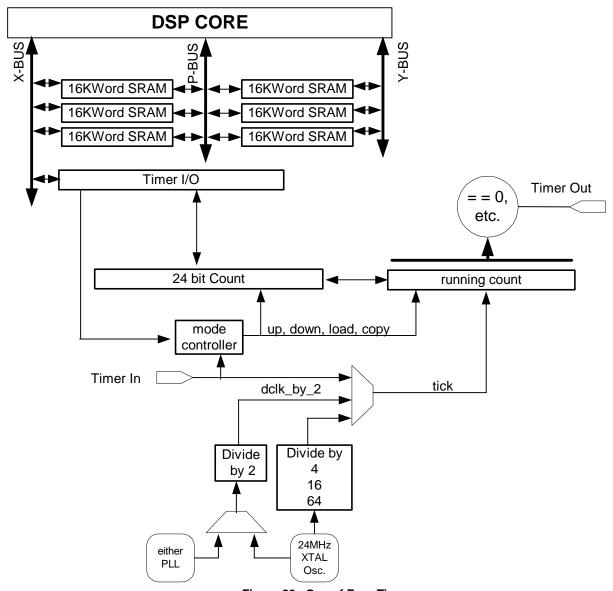

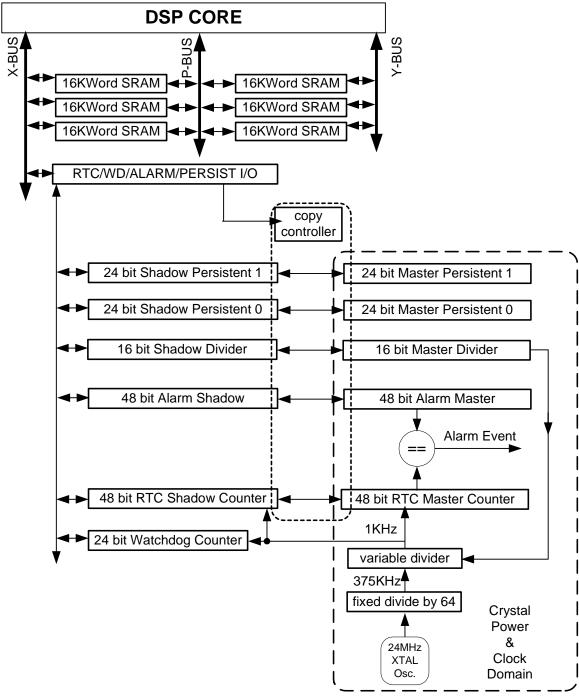

#### 2.3.1. DSP Core

The on-chip DSP core is modeled exactly after the Motorola DSP56004. It supports the identical instruction set, registers, addressing modes, etc., as the DSP56000 family of digital signal processors. Figure 3 shows a high level view of the DSP core. This architecture is highly optimized for battery operated audio applications. Its 24-bit intrinsic data size provides sufficient precision for high quality audio algorithms while minimizing the number of register and data path signals that must be toggled for any operation. The term "WORD", as used in this data sheet, refers to a 24-bit unit of storage unless otherwise noted.

The functionality that defines the on-chip DSP, is the memory map, interrupt processing, and peripherals it offers.

The integrated DSP comprises three execution units, an interrupt controller and a debug interface. It connects to the rest of the STMP35xx chip via three memory busses, a set of interrupt input signals and various reset and clock inputs. It implements a 3 memory space Harvard architecture, simultaneously referencing an X data element, a Y data element and a program element. These references are conveyed over the program or "P" bus, the X bus and the Y bus. Each bus comprises a 24 bit wide data path and a 16 bit address bus. Program accessible I/O registers reside in the top 4K word addresses on the X-bus. The DSP architecture has special programmed I/O support for the top 64 words of this space but SigmaTel has extended this space to the top 4K words, i.e. addresses \$F000 through \$FFFF, inclusive.

The DSP Core also implements the OnCE debugger that is the norm for this DSP architecture. The OnCE interface connects to an external debugger over four I/O signal pins on the STMP35xx.

Using an industry standard instruction set architecture and debugger interface for the integrated DSP means that development tools and debuggers are in the highly evolved and stable portion of their life cycle. In addition, it means that system devel-

5-35xx-D1-1.03-091703 5

# D-Major™Audio System on Chip

Figure 3. DSP Core at a Glance

opers with experience developing on this DSP can be found. The SigmaTel software developers kit (SDK) provides an excellent integrated development environment with an assembler, C compiler, debugger and other requisite tools.

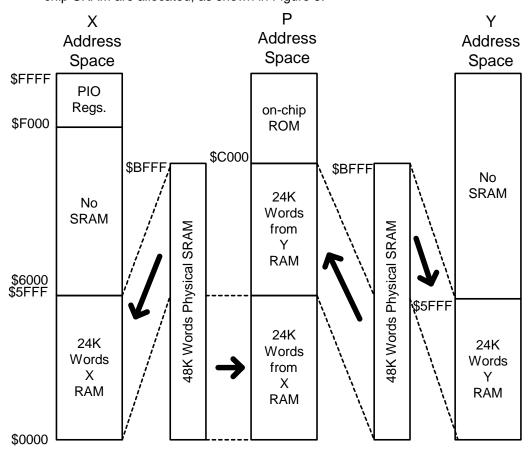

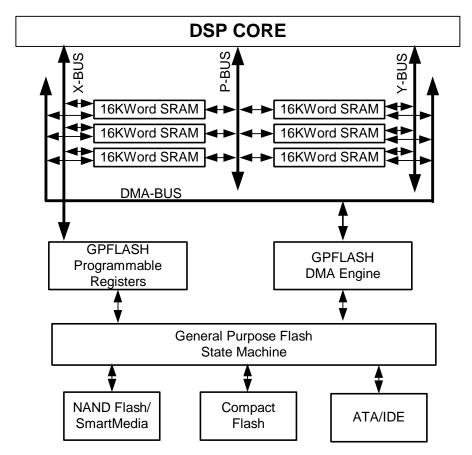

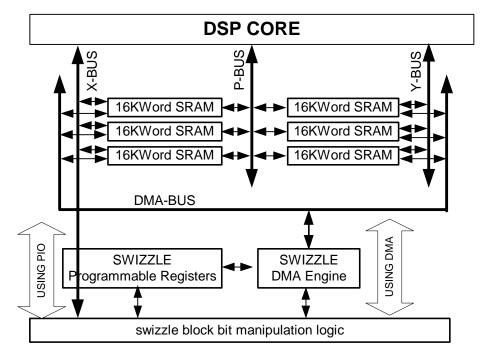

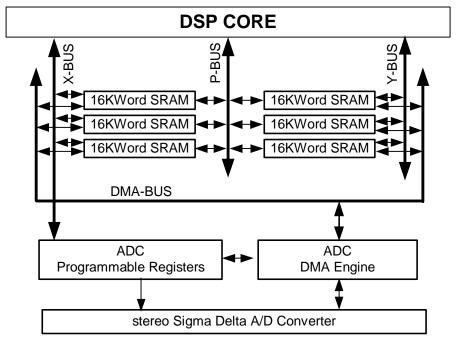

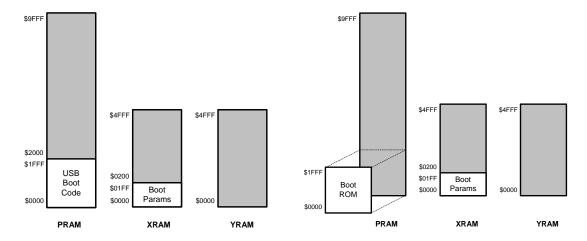

## 2.3.2. On-chip RAM and ROM

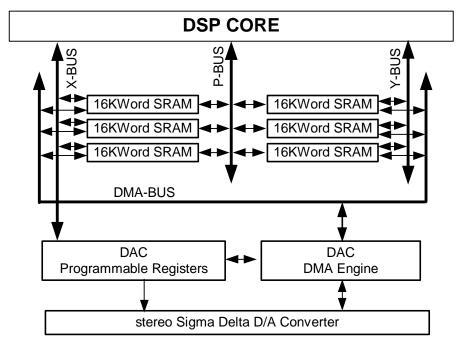

The STMP35xx includes 96K words of on-chip RAM. This amounts to 2.25Mbits of on-chip SRAM in six 16K Word blocks. The RAM is split into two 48K word banks with one bank attached to the X bus and one attached to the Y bus. The P bus is

Figure 4. 6 x 16K Word On-chip SRAM Blocks

connected to both RAM banks so that program space can be allocated from the same two banks that hold X and Y data values. An adjustable switching mechanism

is provided so that a portion of the X bus RAM or Y bus RAM can be allocated to the P bus in units of 8K words from 0K to the full 64K words.

A typical application will allocate a portion of the X bus RAM and another portion of the Y bus RAM to the P bus. In normal operation, this switching mechanism will present a contiguous block of RAM beginning at location zero in the P bus address space, or P:\$0000 as it is written in assembler syntax

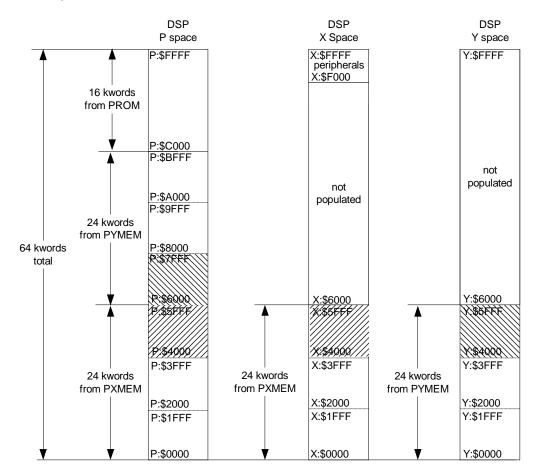

Suppose we allocate 24K Words from the X bus RAM to the P bus and another 24K Words from the Y bus RAM to the P Bus. This gives us 24K Words of X RAM, 24K Words of Y RAM and 48K Words of P RAM for our application. All 96K Words of on-chip SRAM are allocated, as shown in Figure 5.

Figure 5. On-Chip RAM Allocation Example

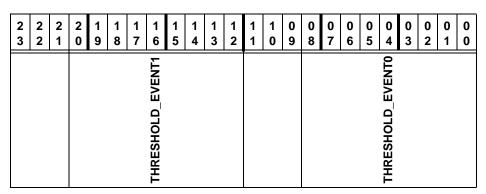

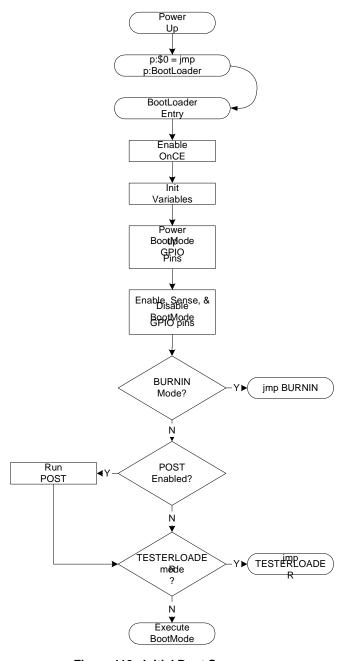

The STMP35xx contains an on-chip 16K Word ROM which holds the Bootstrap code. At power-on time, the first instruction executed by the DSP comes from this ROM. Power-on reset causes the on-chip ROM to be placed at P:\$0000. The reset interrupt vector is located at P:\$0000, thus the first instructions executed come from this ROM. Software in this ROM offers a large number of BOOT configuration options, including manufacturing boot modes for "burn-in" and "tester" operation.

Other boot modes are responsible for loading application code from off-chip into the on-chip RAM. Off chip sources for application bootstrapping include:

- External NAND FLASH

- · Host (PC) controlled bootstrapping using USB,

5-35xx-D1-1.03-091703 7

# D-Major™Audio System on Chip

- Host (PC) controlled bootstrapping using I<sup>2</sup>C slave.

- I<sup>2</sup>C Master transfers from serial EEPROM

Once the on-chip boot code has loaded the application code into on-chip RAM, it can relocate the 16K Word on-chip ROM to the very top of the P address space, see Figure 5. "On-Chip RAM Allocation Example" on page 7. The on-chip ROM can be disabled entirely so that all 64K words of P space is available for on-chip RAM.

The on-chip boot code includes a firmware recovery mode. If the device fails to boot from NAND flash, for example, the device will boot from a PC host connected to its USB port. This firmware recovery mode can be invoked at anytime by holding the PSWITCH or "play" button for at least five seconds during power up.

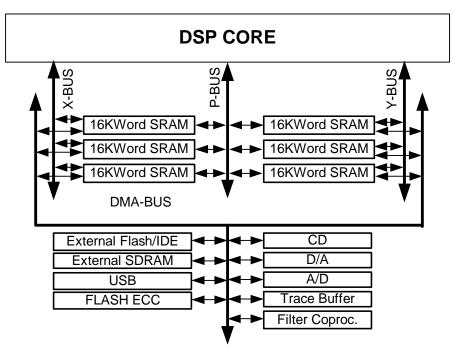

The on-chip RAM serves as one end of all DMA transfers, e.g either the source or destination. Every SRAM block has three potential accessors: P-BUS, DMA-BUS, and its respective X-BUS or Y-BUS. A number of the integrated peripheral controllers use a distributed DMA implementation to transfer data to or from on-chip SRAM.

Figure 6. On-Chip RAM & Distributed DMA

In this distributed DMA architecture, all of the peripheral controllers that use DMA share a common DMA address and data bus path to and from on-chip RAM. Each peripheral controller implements its own address generator. Address generation can be highly sequential as in the case of the D/A converter or fairly random as in the case of the USB controller. Thus each device that uses the distributed DMA will have at least one base address register (HW\_xxxBAR) and various address modifying registers. Most of the distributed DMA devices implement some form of circular buffering in their addressing modes. There is a centralized arbiter that selects which of the distributed DMA peripheral controllers has access to the DMA bus on any given clock cycle.

# D-Major™Audio System on Chip

With a DSP core clock of 65MHz, a single block of on-chip RAM can provide 65MHz times 3 bytes or 195 MByte/second of bandwidth. There are four 24 bit data busses connected to the on-chip SRAM blocks. Furthermore, each SRAM block is single ported and has its own independent address and data busses. Thanks to the arbitration logic in this memory subsystem, all four busses (P, X, Y, DMA) can be made to cycle on every clock. Thus the peak bandwidth available from the on-chip RAM is four times 195 MByte/second or 780 MByte/second.

Of course, there are times when more than one data bus needs to transfer into or out of the same SRAM block. When conflicts occur, the arbiter will "stall" the DSP for one (or more) clock(s) to resolve the conflict.

The reader should not be surprised to see devices like A/D or D/A converters using DMA transfers. Some readers may be surprised to learn that external FLASH and external SDRAM are only accessible via the DMA. The external memories are *not* mapped into the "load/store" space of the DSP's instruction set.

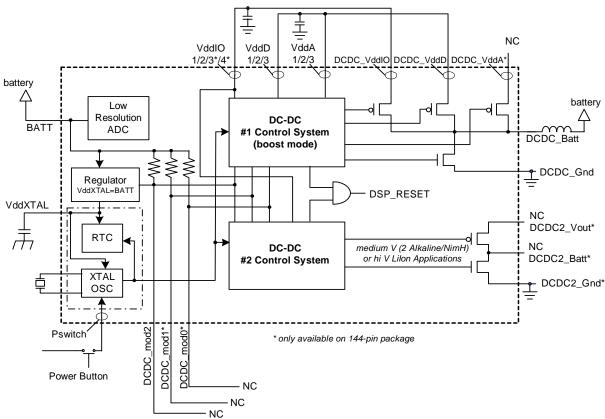

#### 2.3.3. Power Subsystem

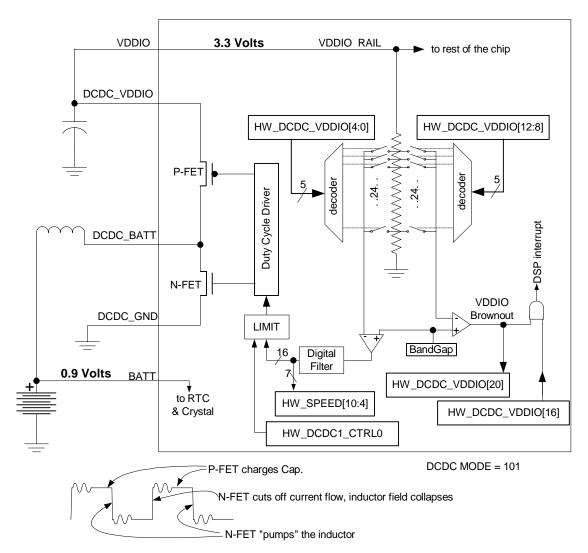

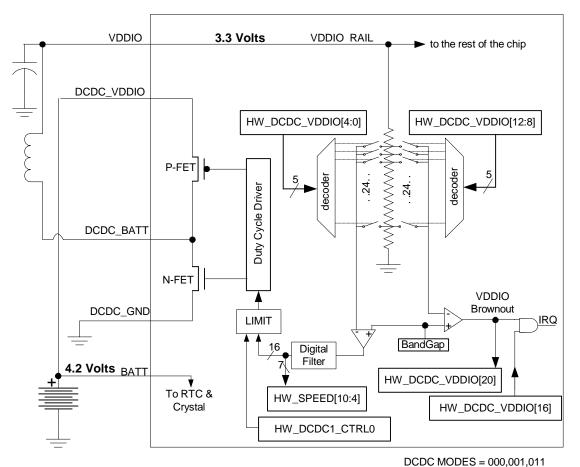

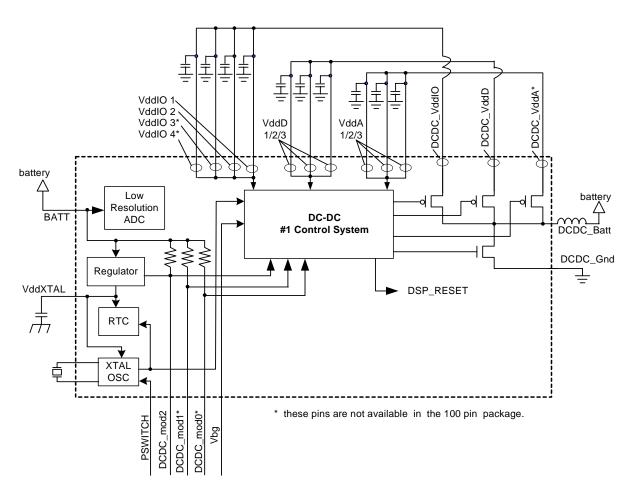

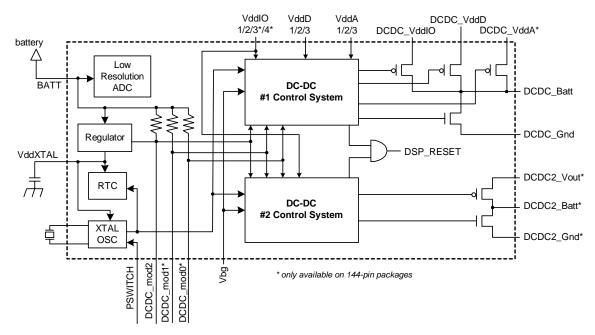

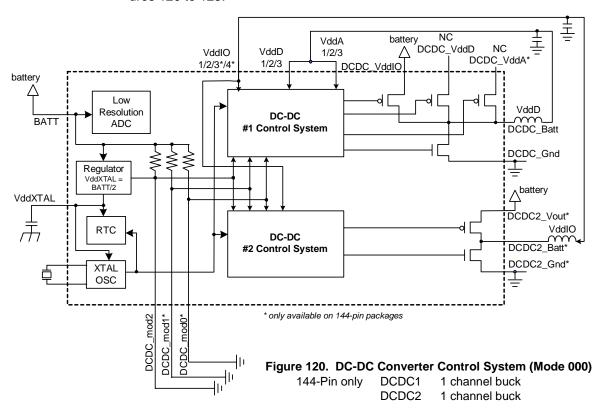

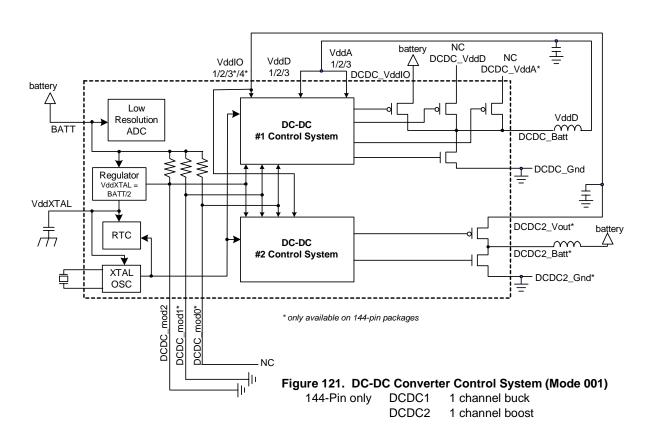

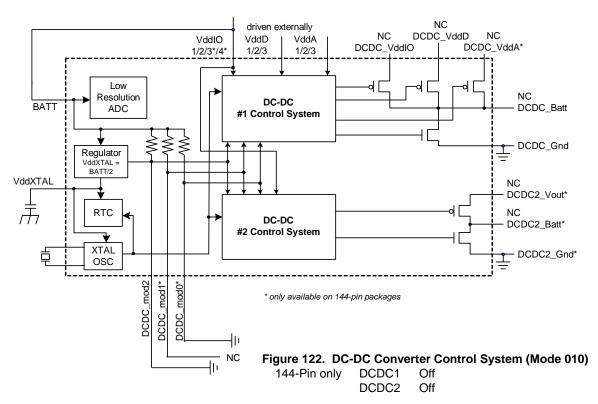

The STMP35xx contains a sophisticated power subsystem including two integrated DC to DC converters to produce a very cost effective product with flexible battery configurations. In addition, it contains power monitoring circuits for battery brownout detection as well as system overload brownout detection. The chip also contains detection circuits for battery installation and removal. It manages power state changes caused by battery changes or from monitoring the on/off power switch circuit.

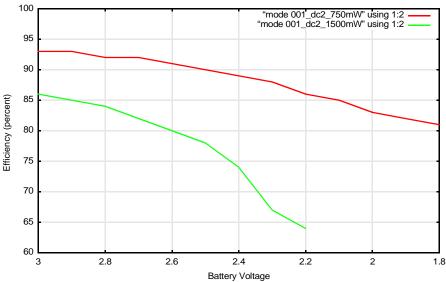

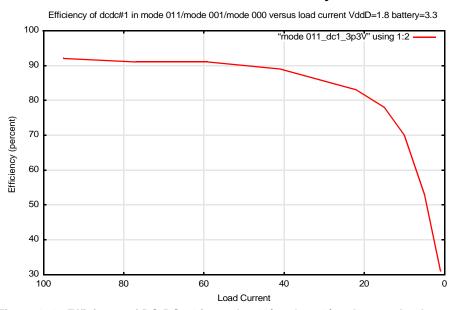

The chip has two programmable integrated DC-DC converters that can be used to provide power for the device as well as the entire application. The converters can be configured to operate from standard battery chemistries in the range of 0.9-4.2 volts including alkaline cells, NiMH, Lilon etc. These converters use off chip reactive components (L/C) in a pulse width or frequency modulated DC to DC converter.

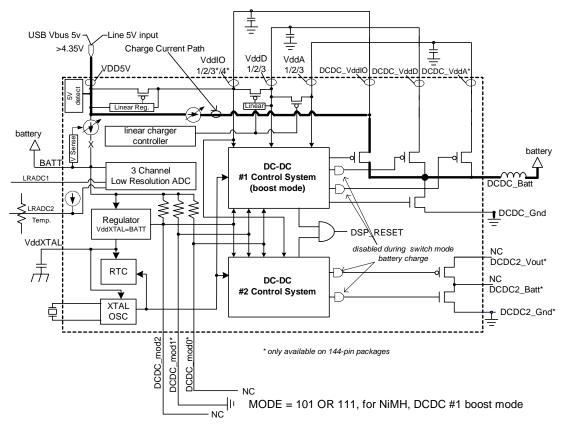

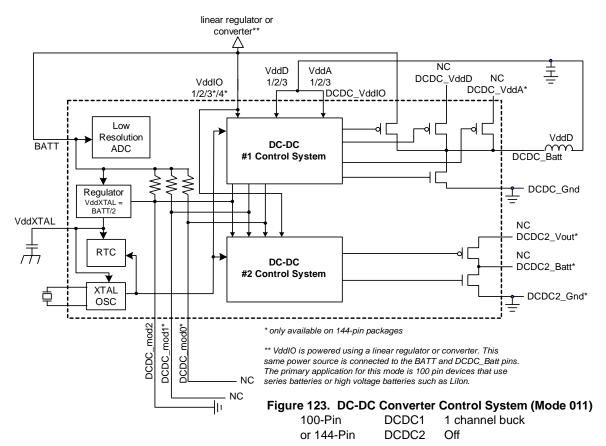

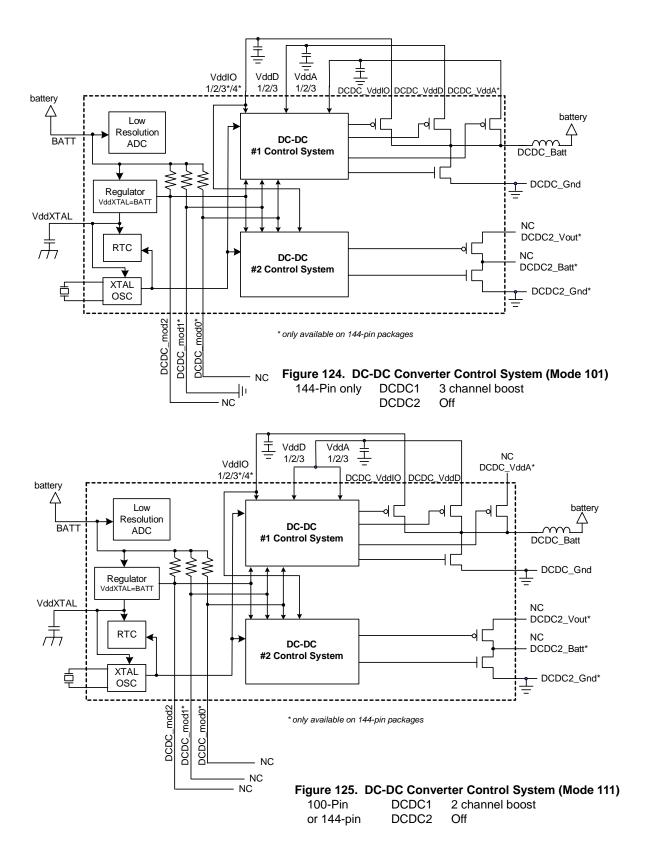

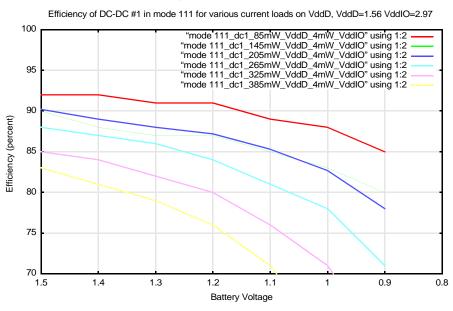

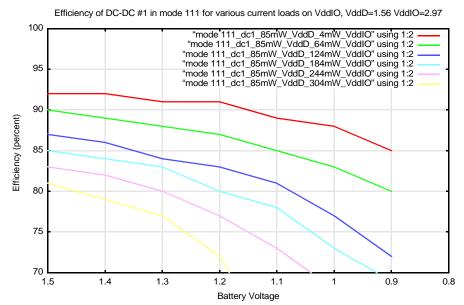

The DC to DC converter circuit consists of the off-chip reactive components, an integrated controller and integrated low resistance FET switches. The DC-DC converter #1, as shown in Figure 7, has one n-channel FET and three independently controlled p-channel FETs generating three independent channels of separately controlled voltages. For the case shown, the battery is a single AA alkaline battery in the range 0.9 to 1.5 volts. DC-DC converter #1 is used to "boost" this input voltage to 3.3 volts for use in driving the I/O VDD rail and two separate 1.8 volt sources for driving the analog VDD rail and the digital VDD rail. This case is shown in the first row of Table 1, "Flexible Battery Configurations," on page 11. Other rows show different configurations supported by the DC to DC converters. For example, when the battery chemistry provides an input voltage that is higher than that desired for the I/O rail, digital rail or analog rail, then the DC to DC converters can operate in "buck" mode which provides a regulated output that is lower than its input.

One obvious use for the DCDC converter is in boosting the output of a nearly depleted alkaline battery delivering 0.9 volts up to the regulated 3.3 volt I/O rail voltage and the regulated 1.8 volt digital and core rails. The DCDC converter can also be used to lower the voltage of a 4.2 volt Lilon battery down to the 1.8V digital core and analog rails. Table 1, "Flexible Battery Configurations," on page 11 shows various battery configurations that can be supported.<sup>1</sup>

5-35xx-D1-1.03-091703

\_

<sup>1.</sup>Note VddA3 == VddHP, VddA4== VddPLL. The analog power pair formerly known, in the STMP3410, as VddA2 and VssA2 have been redefined for the STMP35xx as Vdd5V and LRADC2.

# D-Major™Audio System on Chip

In addition, the DCDC converter can regulate these voltages to lower the standard core and I/O values to extend the battery life. Recall that energy consumed in a CMOS AC circuit is proportional to  $V^2$  so this reduction can be quite significant. These program controlled reductions in operating voltage are used in various SigmaTel software applications to provide very long battery life products. The STMP35xx also contains a silicon speed sensor so that each device can tailor its operating voltage to the minimum required for safe operation as constrained by its individual silicon process parameters and junction temperature.

The DC to DC converters control the power up sequence of the device and hold the rest of the chip in reset until the power supplies have stabilized at the correct voltages. The power up sequence begins when the battery is connected to the BATT pin. As shown in Figure 7, the crystal oscillator will begin running as soon as the battery is connected *and* the pswitch is asserted. The crystal oscillator and the real time clock (RTC) can be programmed to continue to operate even when the player is in the off state. The crystal oscillator and RTC are the only drains on the battery in the off state and designed for very small energy consumption. The RTC module includes an alarm function that can be used to "wake-up" the DC to DC converters which will then wake up the rest of the system.

Figure 7. Lowest Cost 1xAA 100-pin Configuration<sup>1</sup>

The power down sequence is also controlled by the DC to DC converters. When a power down event is detected, they return the player to the power off state. In the power off state with non-Lilon chemistries, the I/O Vdd rail is connected to the Battery and the internal VddD and VddA rails are pulled down to ground to minimize

leakage currents. For Lilon mode, the I/O Vdd rail is connected to ground instead of connecting to BATT.

In addition to the various voltage detectors, a power up or power down event can be signaled by the special power switch circuitry in the DC to DC converters. A simple resistor network and momentary contact push button switch is sufficient for player on/off control.

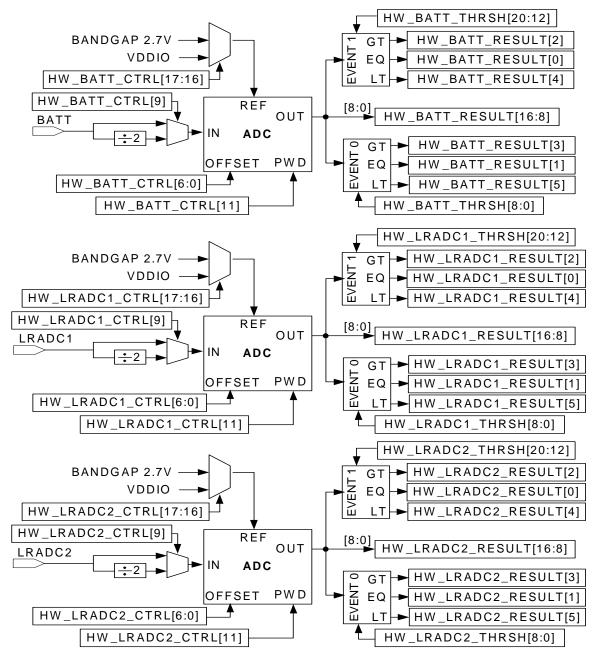

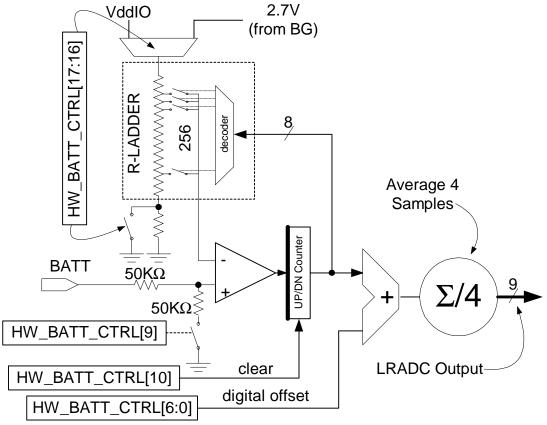

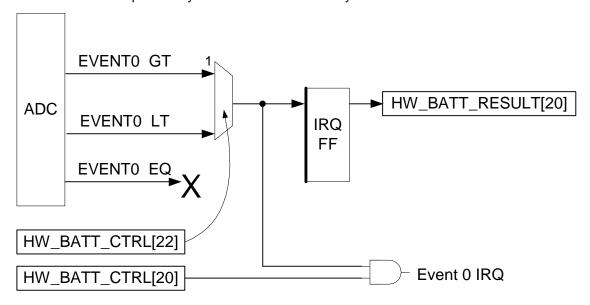

There is a special three channel low resolution A/D converter on-chip to help with battery based applications. One channel is dedicated to measuring the voltage on the BATT pin and is used to monitor the battery condition to estimate its remaining life. All low resolution channel also have digital trip point comparator functions that can be used to generate interrupts to the DSP. The trip point can be programmatically set at one of 512 levels for battery brown out detection on the Battery LRADC or for threshold detection on the other two LRADCs. NOTE: *ONLY* the battery can be connected directly to the BATT pin for correct operation of the device, thus the battery channel of the low resolution A/D converter is not available for any other purpose. The second and third low resolution A/D converters are uncommitted and available for application use. An optional current source can be enabled to either the second or third LRADC pin to support external temperature sensors with minimal external components.

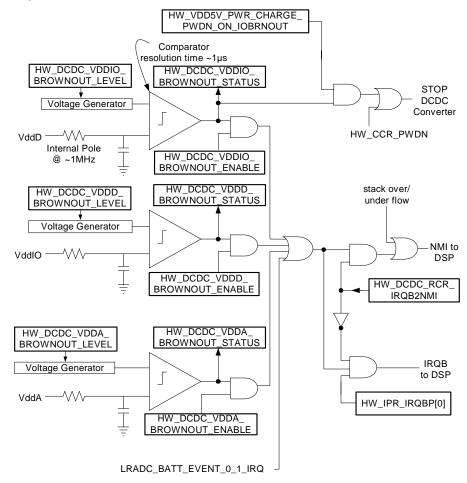

In addition, the DC to DC converters have comparators to monitor their output voltages. They can report "brownout" conditions resulting from over drawing their power capabilities. These conditions are reported either on a normal interrupt level or as a non-maskable interrupt (NMI).

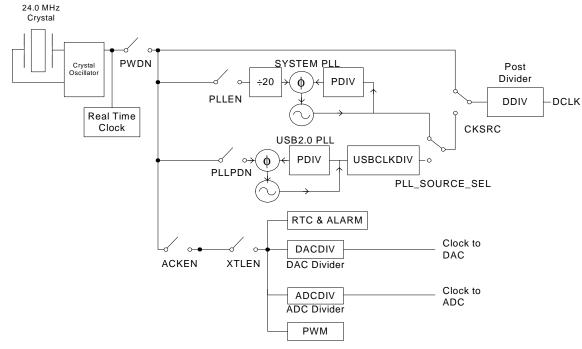

The device contains an integrated PLL which is referenced to the 24.0MHz crystal oscillator. It can generate clock sources from 39.6MHz to 120.0MHz in steps of 1.2MHz. It includes a post divide stage for the digital clock from a divide by one to a divide by 2048. With the PLL turned off and the post divider set to 2048, one can achieve a low power 11.7KHz operating point.

| POWER SOURCE                        | VDD I/O             | VDD D               | VDD A              |

|-------------------------------------|---------------------|---------------------|--------------------|

| 1 Alkaline or 1 NiMH<br>(0.9V-1.5V) | DCDC1<br>DCDC_VddIO | DCDC1<br>DCDC_VddD  | DCDC1<br>DCDC_VddA |

|                                     | Boost<br>3.3V       | Boost<br>1.8V       | Boost<br>1.8V      |

|                                     | 3.3 V               | 1.0 V               | better noise floor |

|                                     |                     |                     | (144-pin)          |

| 1 Alkaline or 1 NiMH                | DCDC1               | DCDC1               | DCDC1              |

| (0.9V-1.5V)                         | DCDC_VddIO          | DCDC_VddD           | DCDC_VddD          |

|                                     | Boost               | Boost               | Boost              |

|                                     | 3.3V                | 1.8V                | 1.8V               |

|                                     |                     | lowest cost (shared |                    |

|                                     |                     | passives & 100-pin) |                    |

| Lilon, (3.0-3.6V)                   | Lilon Battery       | DCDC1               | DCDC1              |

|                                     |                     | Buck                | Buck               |

|                                     |                     | 1.8V                | 1.8V               |

| 2 Alkaline or 2 NiMH                | DCDC2               | DCDC1               | DCDC1              |

| (1.8V-3.0V)                         | Boost               | Buck                | Buck               |

|                                     | 3.3V                | 1.8v                | 1.8V               |

| Lilon (3.3V-4.2V)                   | DCDC2               | DCDC1               | DCDC1              |

|                                     | Buck                | Buck                | Buck               |

|                                     | 3.3V                | 1.8V                | 1.8V               |

**Table 1. Flexible Battery Configurations**

# D-Major™Audio System on Chip

There is an integrated watchdog reset timer available for automatic recovery from catastrophic software errors. If programmed by software, this circuit will generate a reset sequence if its timer is ever allowed to reach zero. Normally functioning software will reload the watchdog count before expiration of the count. The maximum delay until a watchdog reset is greater than four hours.

### 2.3.4. Battery Chargers

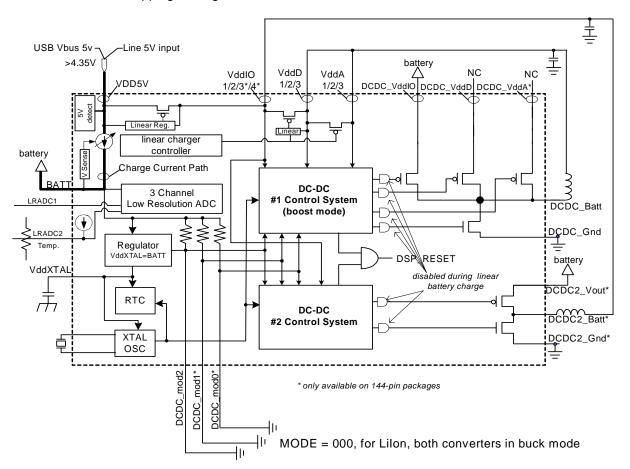

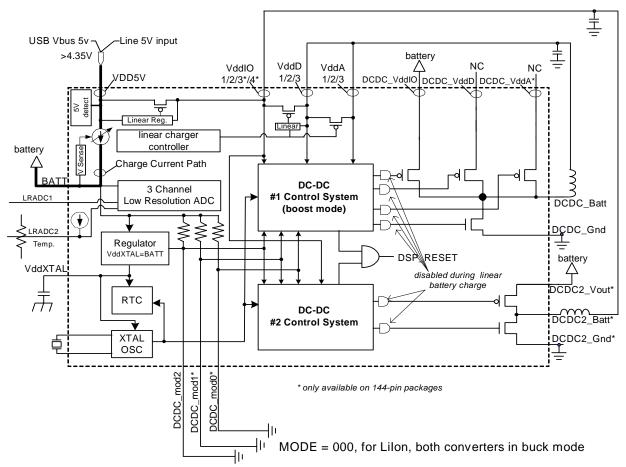

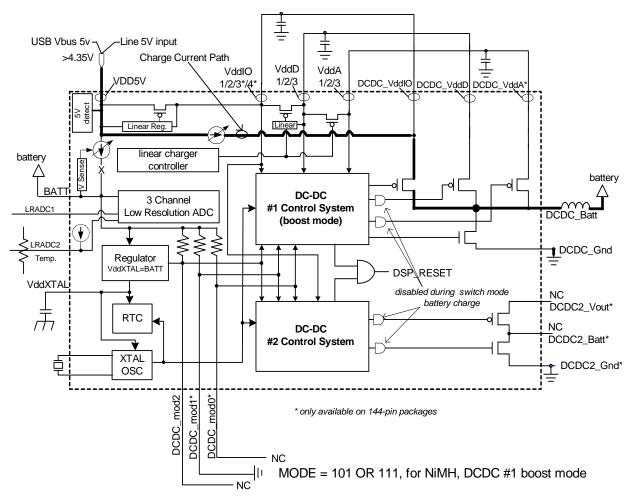

Figure 8 shows additional detail to the DCDC converter circuit of Figure 7 which supports NiMH battery charging in a USB or AC line attached environment. In this case, 5 V is brought into the STMP35xx on the charger pin (VDD5V). A pair of onchip linear regulators drop the incoming voltage to 3.3V for the I/O circuits and 1.8V for the digital and analog core. Additional mux (pass) transistors have been added to allow internal switching and routing of the line supplied voltage so that the I/O, digital and analog supply needs of the chip are met from the line voltage. Additional mux transistors isolate the battery pin so that it can receive charge current from the DCDC\_BAT pin. The charging current path is shown as a very bold line overlaying the block diagram. The linear charger controlled current source and the DCDC converter #1 precisely controls the charging current to the program specified amount. The battery channel of the low resolution ADC is used to monitor the charging progress of the NiMH battery.

Figure 8. Integrated NiMH Battery Charger

A thermo-sensor can be attached to the second or third channel of the LRADC so that battery temperature can be monitored by software for an optimal charging cycle. Finally, software can make use of the RTC alarm function to periodically wake

up and check the charge progress. Most of the better NiMH charging protocols can be implemented in this fashion.

The STMP35xx also integrates support for Lilon charging protocols in USB or AC line attached environments. When the 5 V source is detected on the VDD5V pin the power management system automatically reconfigures to use the integrated linear regulators to supply the core and I/O rails. Software can then enable the integrated current source to provide battery charge current, as shown by the bold path in Figure 9. The variable current sources tappers of the charge current as it approaches the maximum Lilon battery voltage. Software can then take over to control the final "topping-off" algorithm, as desired.

Figure 9. Integrated Lilon Battery Charger

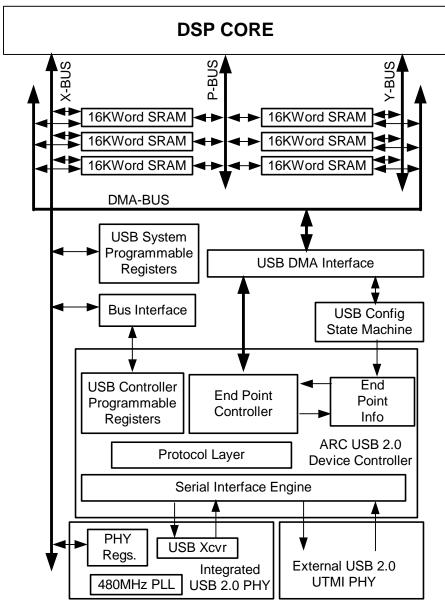

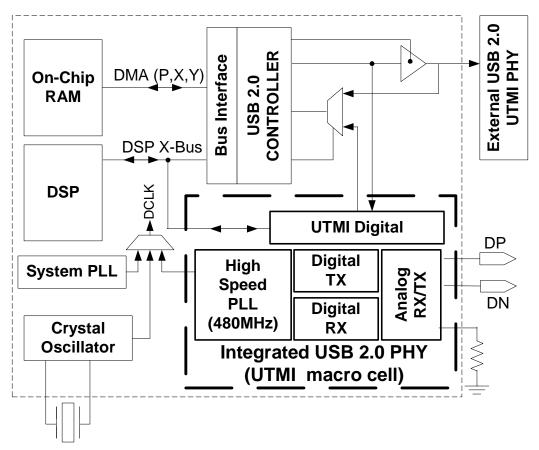

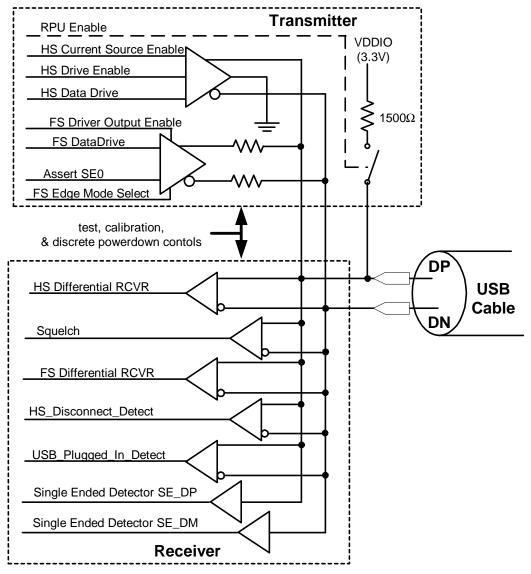

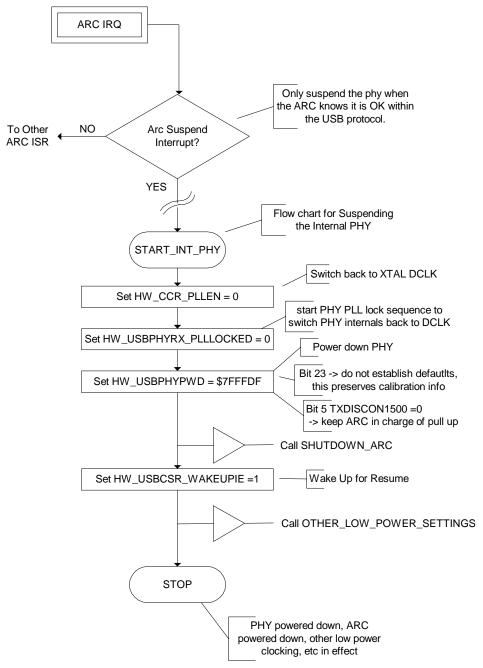

#### 2.3.5. USB Interface

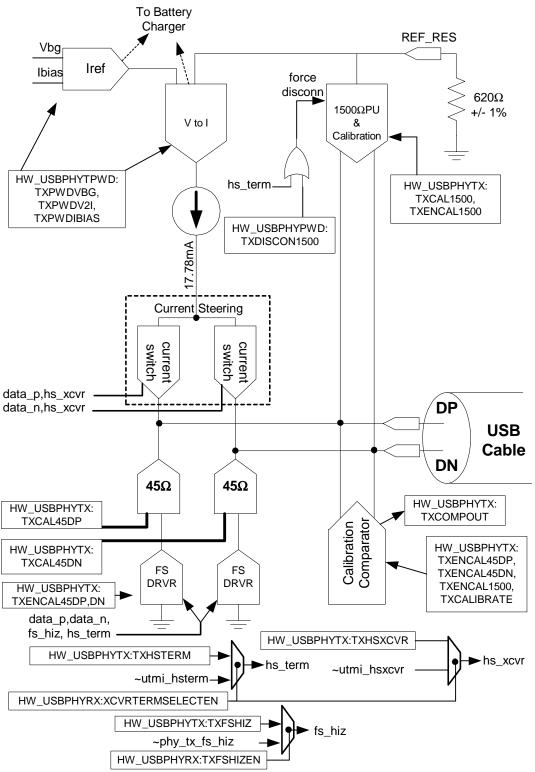

The chip includes a Universal Serial Bus (USB) version 2.0 controller and integrated UTMI PHY. The STMP35xx device interface can be attached to USB 2.0 hosts and hubs running in the USB 2.0 High Speed mode at 480Mbit/second. It can be attached to USB 2.0 Full Speed interfaces at 12Mbit/second. Of course, the USB 2.0 Full Speed mode allows the STMP35xx to attach to USB 1.1 compliant hosts and hubs.

# D-Major™Audio System on Chip

The USB interface is used to download digital music data or program code into external memory and to upload voice recordings or MP3 encoded recordings from external memory to the PC. Program updates can also be loaded into the flash memory area using the USB interface.

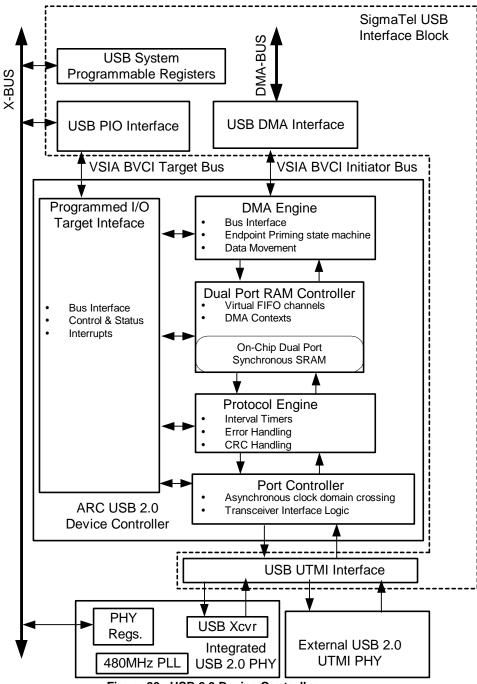

Figure 10. USB Interface Block Diagram

The Universal Serial Bus (USB) is a cable bus that supports data exchange between a host computer and a wide range of simultaneously accessible peripherals. The attached peripherals share USB bandwidth through a host-scheduled, token based protocol. The bus allows perpherals to be attached, configured, used and detached while the host and other peripherals are in operation.

The USB subsystem is designed to make efficient use of system resources within the SMTP35xx. It contains a random access DMA engine that reduces the interrupt

load on the DSP and reduces the total bus bandwidth that must be dedicated to servicing the eight on-chip physical endpoints

It is a dynamically configured port which can support up to 6 general use physical endpoints and 8 logical endpoints, each of which may be configured for bulk, interrupt or isochronous transfers. The USB configuration information is read from on-chip memory via the USB controller's DMA.

Figure 10 shows a block diagram of the USB controller. This device makes extensive use of the DMA to read and write the multiple buffers associated with all of the endpoints that it can have open at one time

#### 2.3.6. External Memory Interfaces.

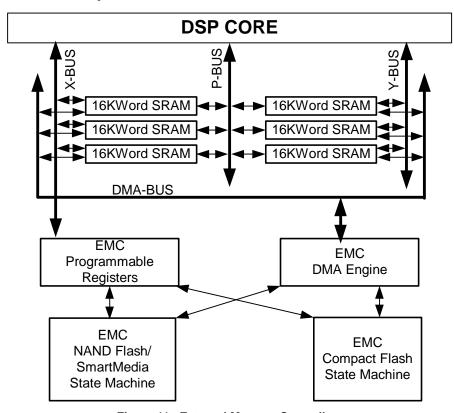

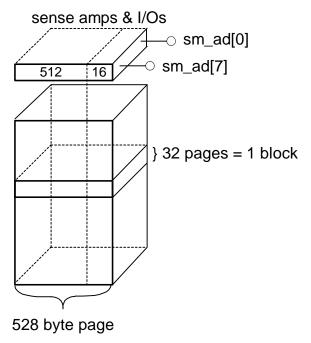

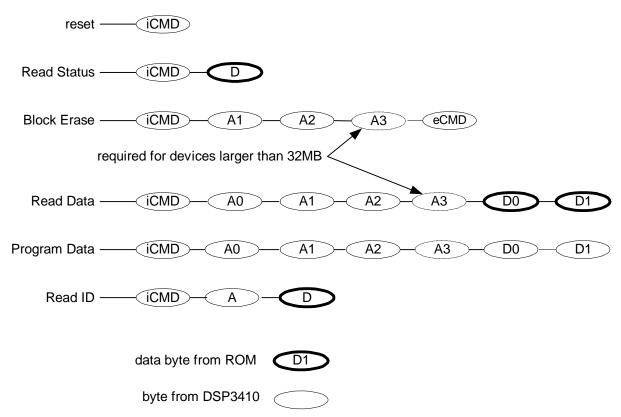

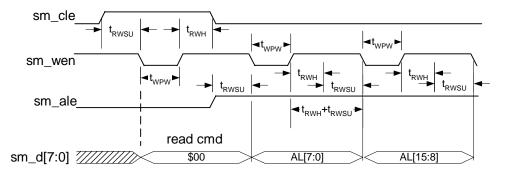

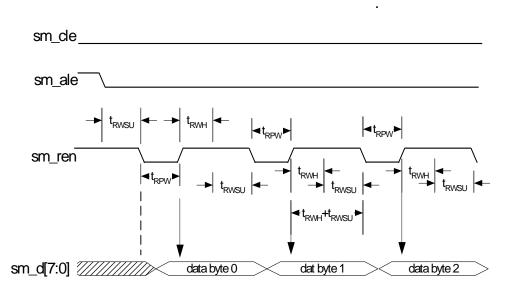

Figure 11. External Memory Controller

The chip includes an external memory controller that has two major functional modes: SmartMedia/NAND and CompactFlash. The SmartMedia/NAND flash interface provides a state machine that provides all of the logic necessary to perform DMA functions between on-chip RAM and the flash. The CompactFlash interface supports all three major CompactFlash modes: Memory, I/O and IDE. These modes can be used to communicate with standard CompactFlash (CF) devices such as CF Flash and the IBM MicroDrive. The CF Memory mode can be used to communicate with standard ATA/ATAPI devices like CD-ROM and Hard drives

The external memory controller can be described as three fairly independent devices in one: a SmartMedia/NAND flash interface based on the STMP3410 flash controller, a CompactFlash/NOR flash/IDE interface, and a new general purpose flash state machine that can support the new 1Gb/die NAND flash devices with

# D-Major™Audio System on Chip

128KByte block erase modes. These interfaces share the same device pins, some registers and the DMA engine.

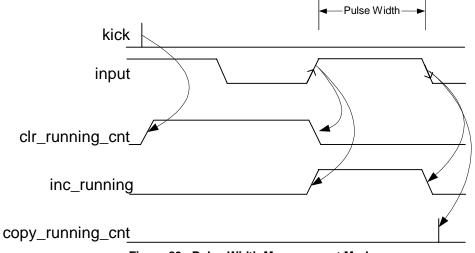

The interfaces use memory mapped registers to setup and control the transactions. Data is always sent through DMA – there are no data registers that correspond to the interface data bus. Transactions are always started with a kick bit. The interface sets up the control lines and transfers data to/from the internal RAM. Once the transaction is complete the interface signals the DSP with either a polled flag or an interrupt.

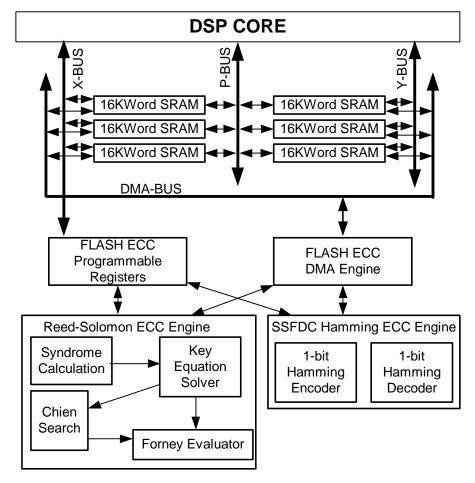

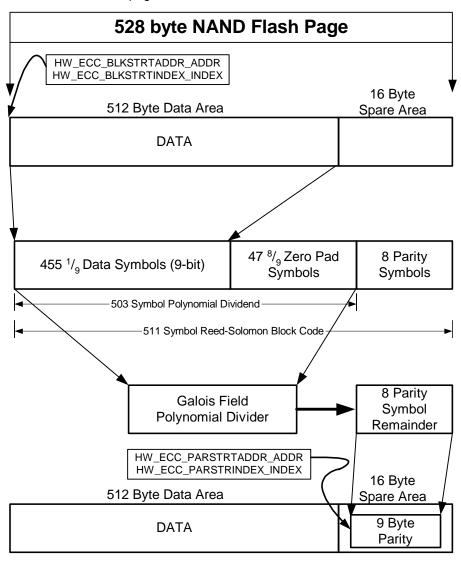

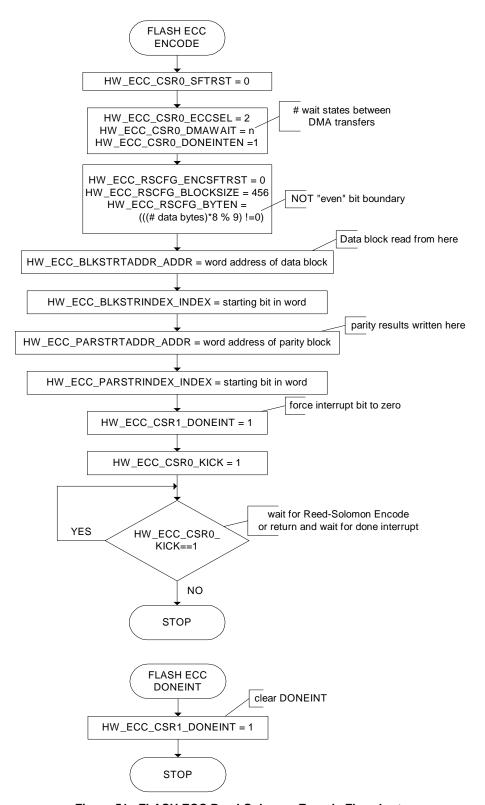

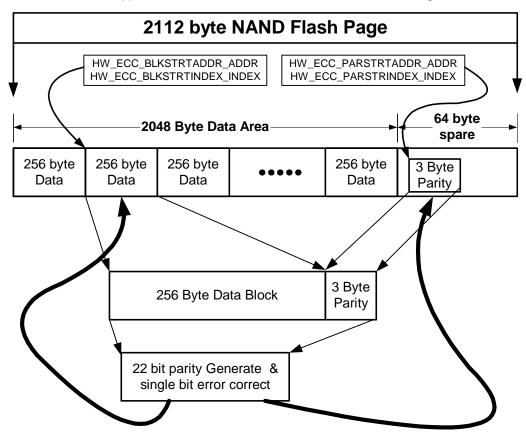

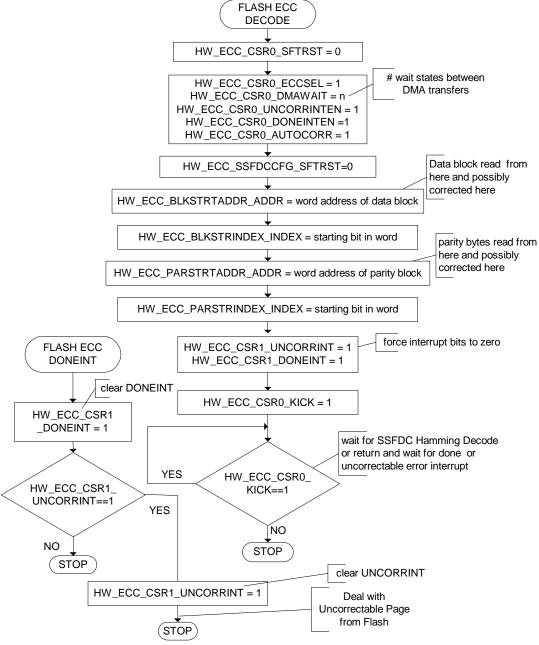

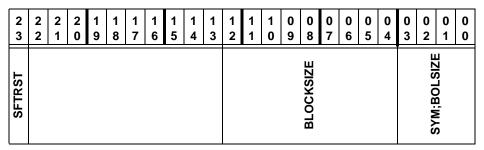

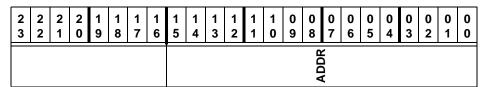

#### 2.3.7. Hardware Acceleration for ECC for Robust External Storage

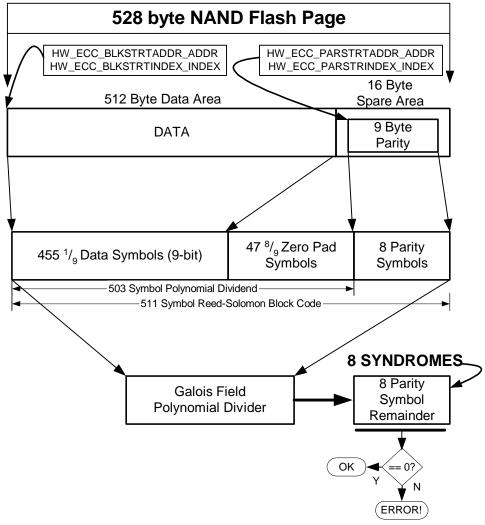

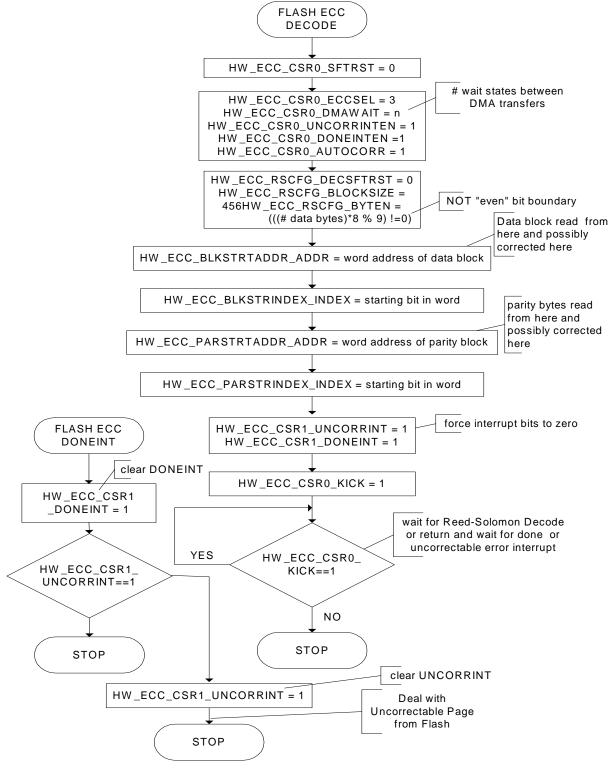

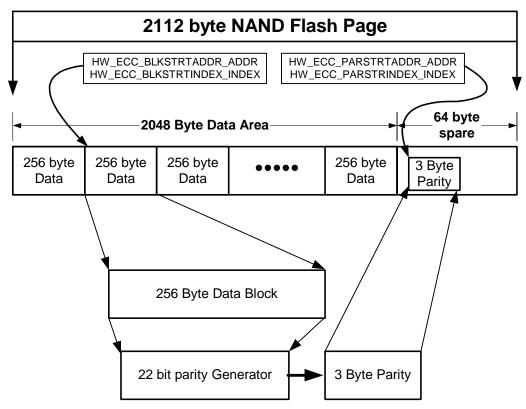

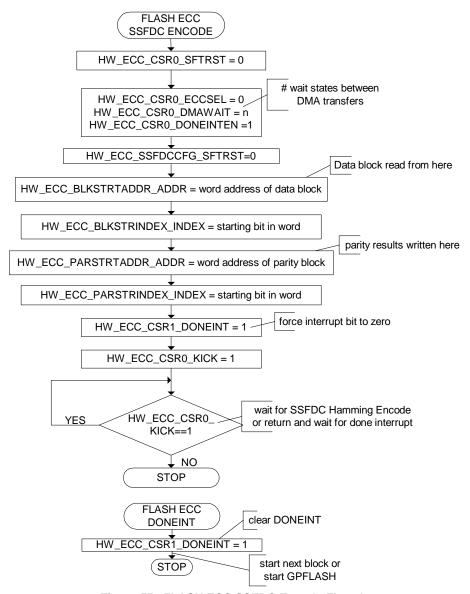

The forward error correction module is used to provide STMP35xx applications with a reliable interface to various storage media, especially storage media that would otherwise have unacceptable bit error rates. The ECC module comprises two different error correcting code processors:

- 1-bit correcting Samsung SSFDC (Hamming-code) encoder/decoder.

- 4-symbol correcting (9-bits/symbol) Reed-Solomon encoder/decoder.

The 1-bit hamming code is defined by Samsung for use with all SSSFDC compliant NAND flash memories. This code is capable of correcting a single incorrect bit over the block for which the ECC is valid (256 bytes per page).

The purpose of the Reed-Solomon decoder is to process a coded block (data block followed by "parity" check data) to determine if there is an error and, if there are errors, where they are located and how to correct them. The purpose of the Reed-Solomon encoder is to read a block of 503-symbols from RAM, calculate and append 8-parity symbols to form a 512-symbol RS-codeword.

The Hamming code error corrector is strong enough to detect two bits in error in 256 bytes and to correct 1-bit/256 byte errors. Both of these error correction encoder/decoders use DMA transfers to move data to and from on-chip RAM completely in parallel with the DSP performing other useful work.

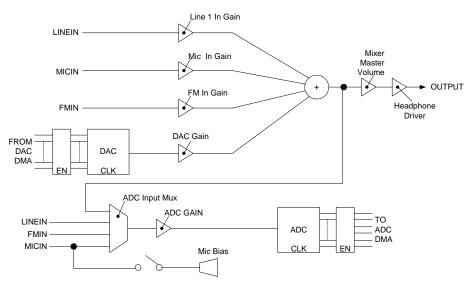

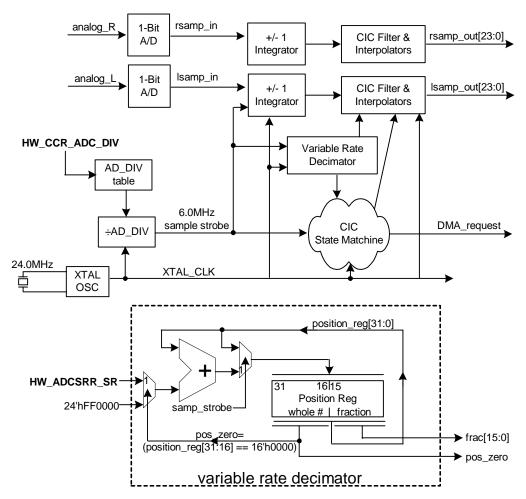

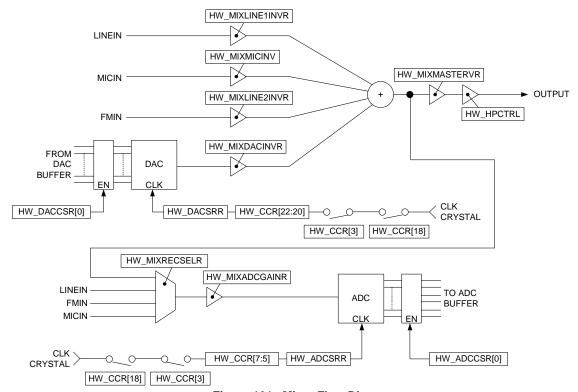

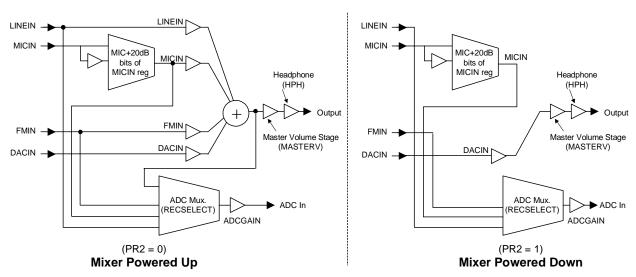

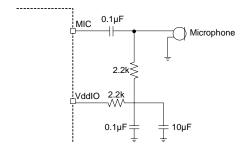

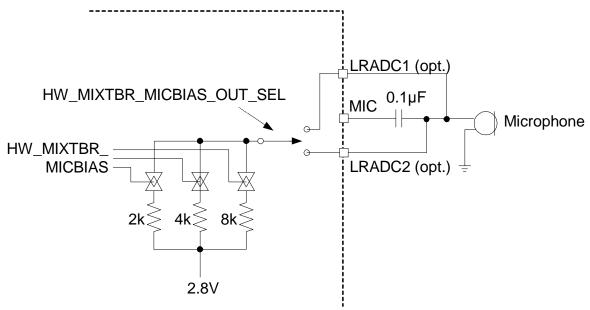

#### 2.3.8. Mixed Signal Audio Subsystem

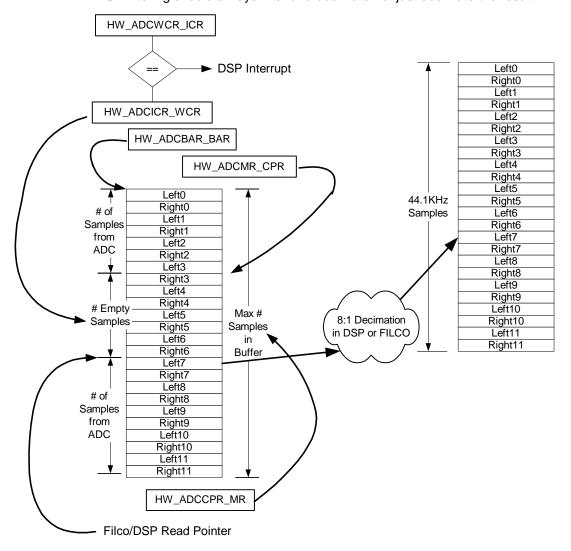

The STMP35xx contains an integrated high quality mixed signal audio subsystem, including high quality sigma delta D/A and A/D converters. The D/A is of course the mainstay of the Audio Decoder/Player product application while the A/D is used for Voice Record and MP3 Encode applications.

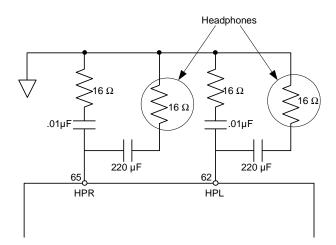

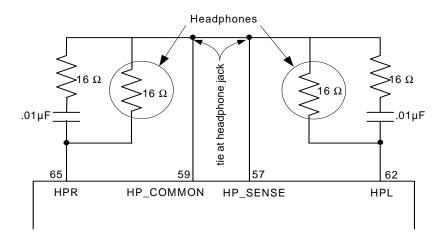

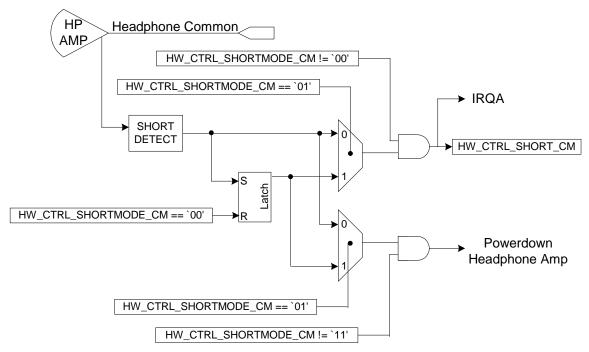

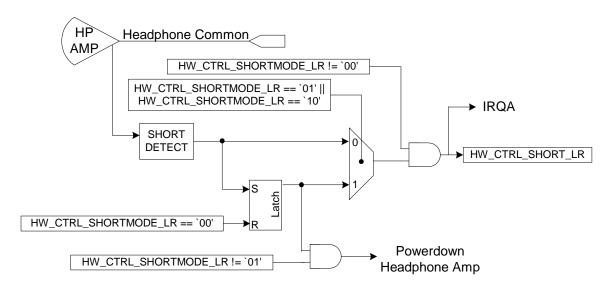

The chip includes a low noise headphone driver that allows it to directly drive low impedance ( $8\Omega$  or  $16\Omega$ ) headphones. The direct drive, or "cap-less" mode removes the need for large expensive DC blocking capacitors in the headphone circuit. The headphone power amplifier can detect headphone shorts and report them via the DSP interrupt system. A digitally programmable master volume control allows user control of the headphone volume. Annoying clicks and pops are eliminated by zero crossing updates in the volume/mute circuits and by headphone driver startup and shutdown circuits.

There is an integrated analog mixer that drives the master volume control programmable gain amplifier. The chip provides for two stereo line level inputs and a mono microphone input. The microphone circuit has a mono to stereo programmable gain pre-amp and an optional microphone bias generator. The line inputs have programmable gain/attenuation and balance capability. The integrated sigma delta DAC has a programmable gain/attenuation analog amplifier. The programmable gain/attenuation stage outputs from all three stereo inputs and from the DAC are mixed together

# D-Major™Audio System on Chip

to drive the master volume control. There is an analog mux in front of the ADC that can select any of the three input sources or the mixer output. The selected source is then sent to the ADC Gain stage and from there to the ADC. The mixer can be independently powered down. In this configuration, the mixer is bypassed so that the DAC can still play audio through the headphone driver saving power consumption and improving the SNR and THD performance.

Figure 12. Mixed Signal Audio Elements

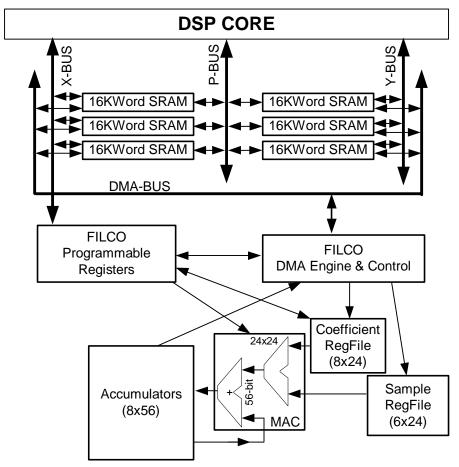

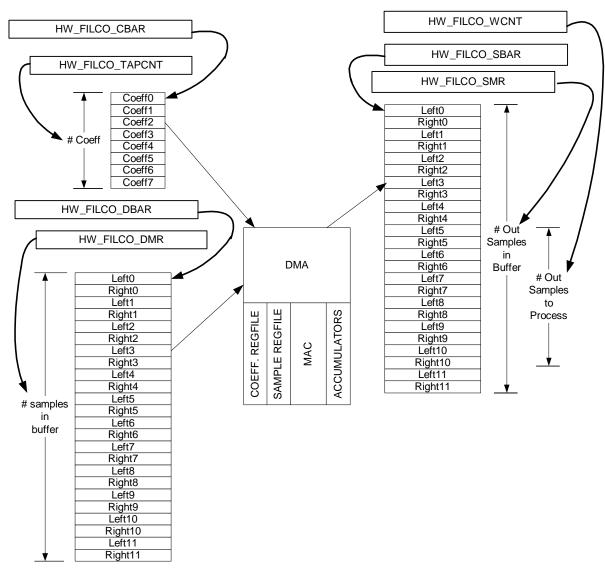

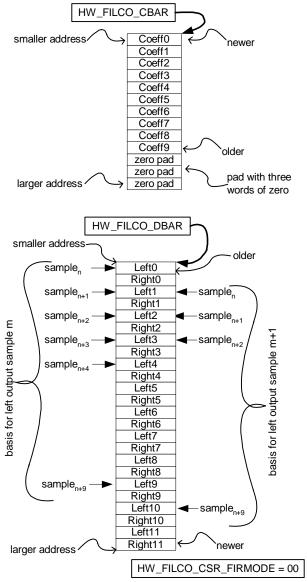

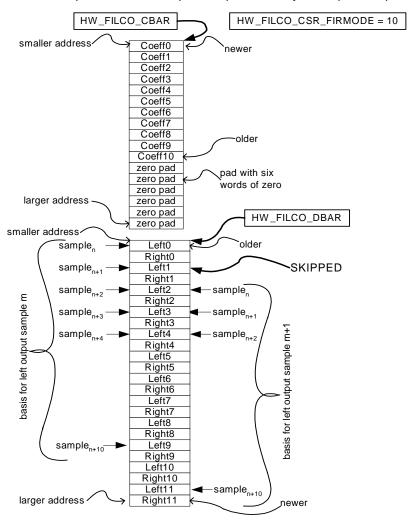

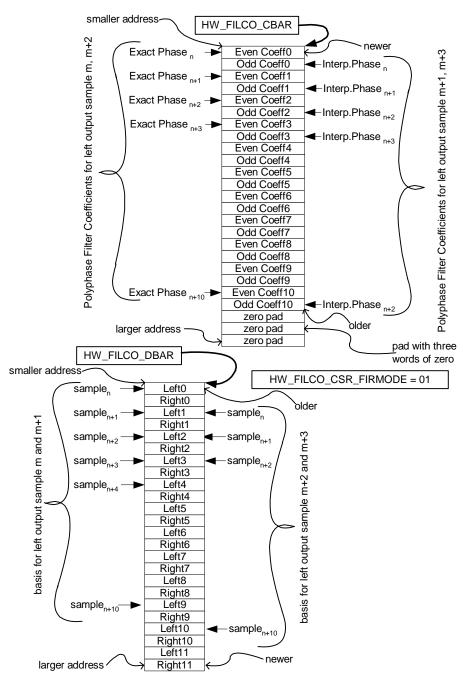

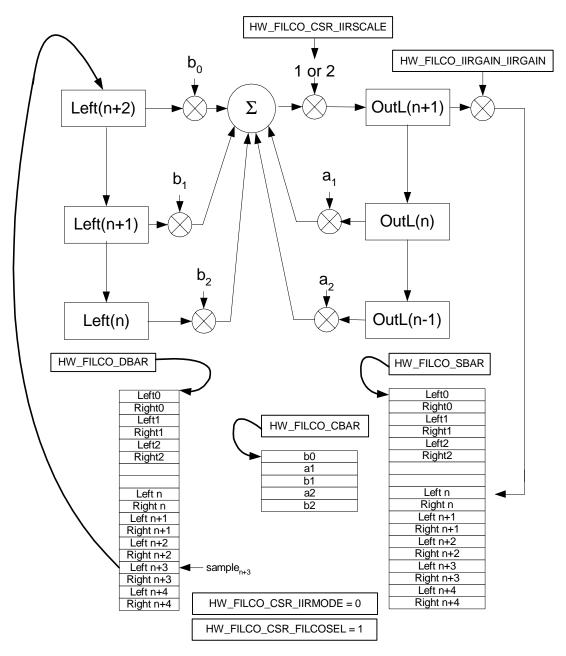

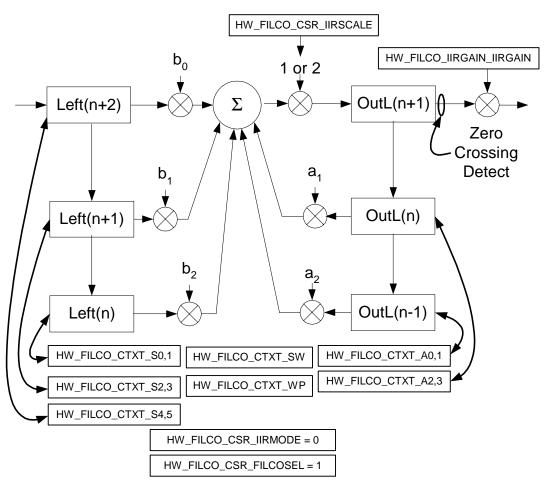

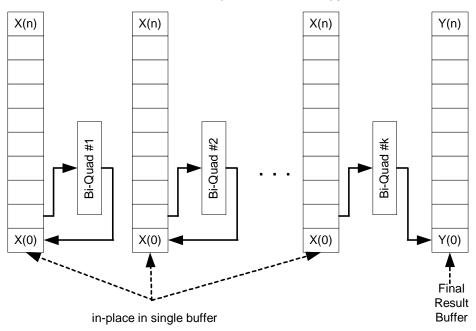

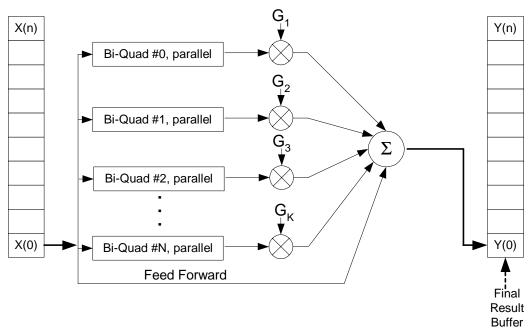

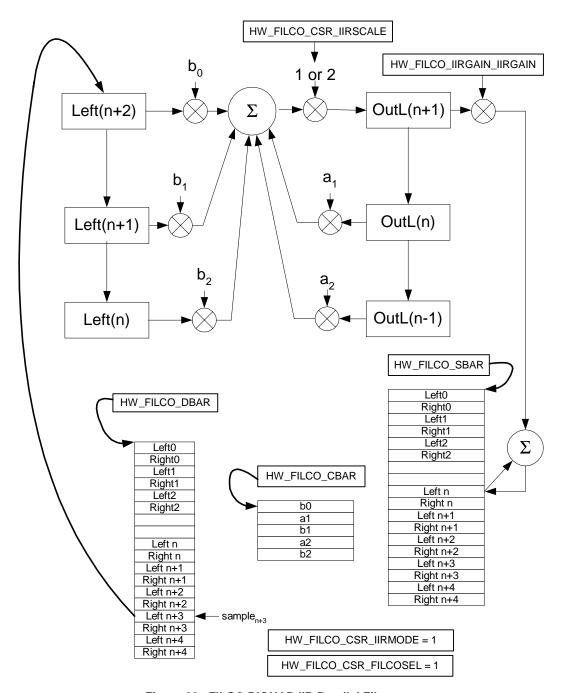

#### 2.3.9. Filter Coprocessor

A filter coprocessor has been added to the STMP35xx to reduce the DSP load associated with filter calculations. Additional enhancements in the ADC and DAC buffer management have greatly reduced the DSP work load as compared with STMP3410 based applications. The concomitant reduction in DSP overhead yields more available MIPS for more intensive software applications or allows the reduction in clock frequency/voltage and thereby dramatically extends the battery life. The filter coprocessor is a DMA based engine that overlaps execution with the DSP.

#### 2.3.10. IDE/ATA Hard Drive Interface

The external memory controller interface supports the attachment of an ATA/IDE hard drive device. This is particularly useful for one inch 2GByte hard drive and 2.5 inch 10GByte hard drive MP3 players. Hard drive and external SDRAM configurations are supported in the same application, i.e. large blocks of hard drive data can be copied to SDRAM leaving the hard drive unused for most of the MP3 play time.

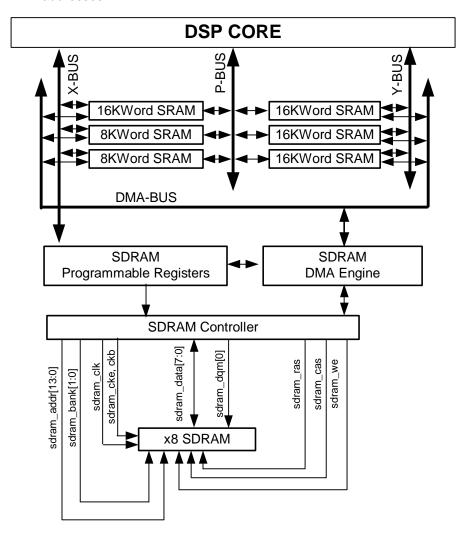

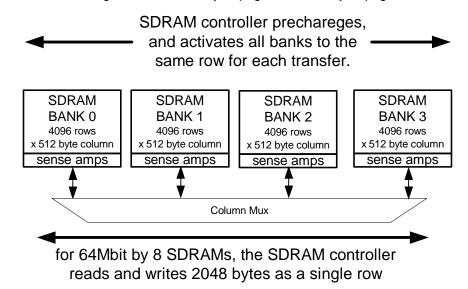

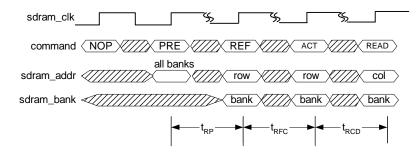

#### 2.3.11. SDRAM Interface

The STMP35xx contains an SDRAM controller that can be used to connect external SDRAM memory chips. The controller is designed to work with 8 bit wide memory systems. It supports SDRAM products from the 64Mbit, 128Mbit and 256MBit JEDEC families. SDRAM memory systems as small as 8MBytes can be configured. SDRAM memory subsystem are useful for applications that include CD-ROM or IDE hard drives.

# D-Major™Audio System on Chip

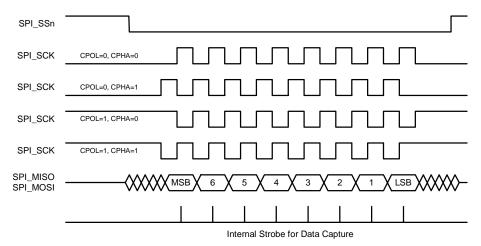

# 2.3.12. Serial Peripheral Control Interface and I<sup>2</sup>C

The chip contains a four wire SPI bus. It can act as a master for this bus to control other chips in the system, such as EEPROMs. It can also act as a slave on this bus to allow a host processor to communicate with the STMP35xx. The STMP35xx includes an enhanced SPI interface that provides DMA transfer support. In addition, the chip contains a two wire SMB/I<sup>2</sup>C bus interface. It can act as either a slave or master on the SMB interface.

#### 2.3.13. LCD/LED and GPIO

The STMP35xx contains 85 GPIO pins in the 144-pin package. Most digital pins that are available for specific functions, e.g. SDRAM interface are also available as GPIO pins if they are not otherwise used in a particular application.

Most LCD and LED displays can be directly controlled from the GPIO interface.

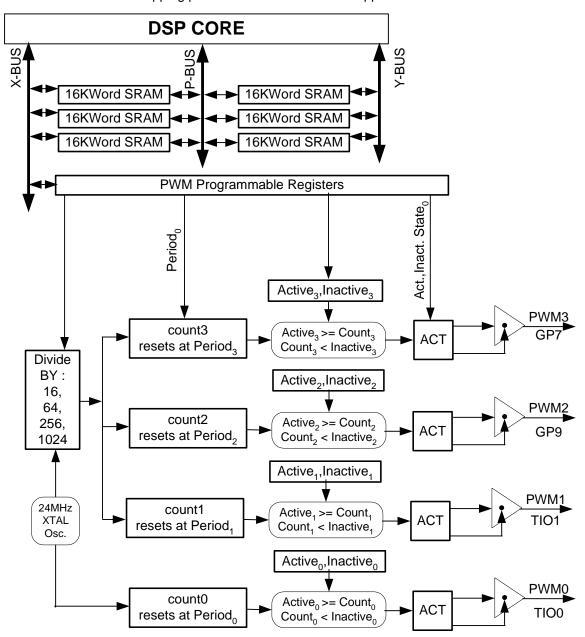

## 2.3.14. PULSE WIDTH MODULATOR (PWM) CONTROLLER

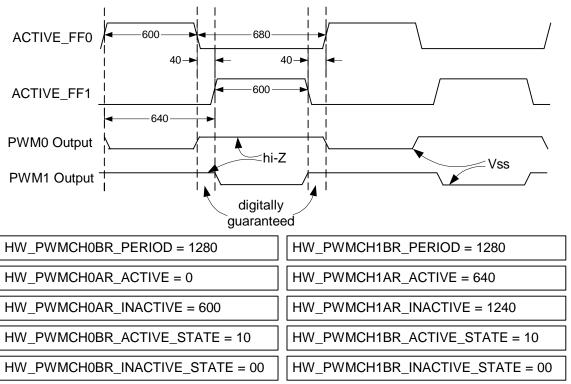

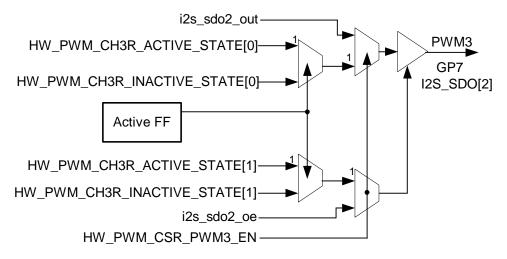

The STMP35xx contains four PWM output controllers that can be used in place of GPIO pins. Applications include LED brightness control and high voltage generators for electroluminescent lamp (E.L.) display back lights. Independent output control of each phase allows zero, one or hi-Z to be independently selected for the active and inactive phases. Individual outputs can be run in lock step with guaranteed non-overlapping portions for differential drive applications.

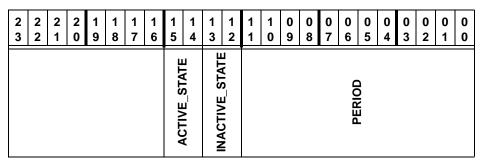

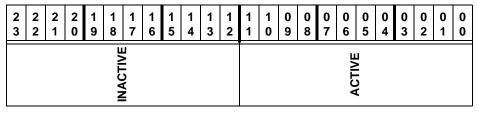

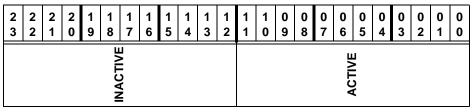

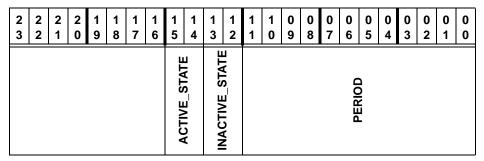

The controller does not use the DMA. Initial values of Period, Active, and Inactive widths are set for each desired channel. The outputs are selected by phase and then the desired PWM channels are simultaneously enabled. This effectively launches the PWM outputs to autonomously drive their loads without further DSP intervention.

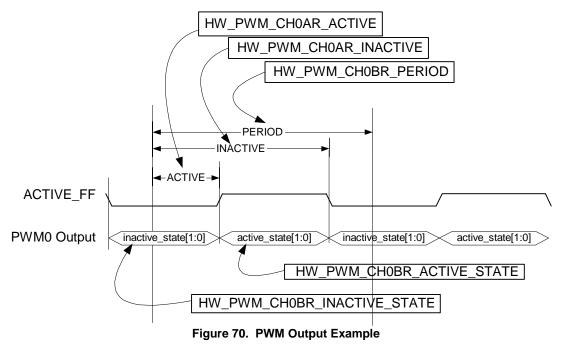

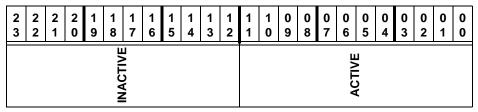

Each PWM channel has a dedicated internal 12 bit counter which increments once for each divided clock period presented from the clock divider. The internal counter resets when it reaches the value stored in the channel control registers. The Active flip flop is set to one when the internal counter reaches the value stored in a register. It remains high until the internal counter exceeds the value stored in another register. These two value define the starting and ending points for the logically "active" portion of the waveform. The actual state on the output for each phase, e.g. active or inactive, is completely controlled by the active and inactive state values in the channel control registers and can be: HIGH, LOW, or TRI-STATE.

# D-Major™Audio System on Chip

# 2.4. Signal Pin Sharing Among Various Application Configurations

A large number of the chips I/.O pins are shared between various functions. The exact conflicts can be found in Table 489, "Pin Definition Table," on page 368.

|                                   | EMC NAND & SmartMedia | EMC CompactFlash Memory & ATA/IDE | SDRAM | CapLess Mode Headphone | Line In 1) |

|-----------------------------------|-----------------------|-----------------------------------|-------|------------------------|------------|

| EMC NAND & SmartMedia             |                       | #2                                | #1    |                        |            |

| EMC CompactFlash memory & ATA/IDE | #2                    |                                   | #1    |                        |            |

| SDRAM                             | #1                    | #1                                |       |                        |            |

| CapLess Mode Headphone            |                       |                                   |       |                        | #3         |

| Line In 1                         |                       |                                   |       | #3                     |            |

| Table 2 Pin Sharing Constrain     | te hy                 | Sube                              | veton | •                      |            |

Table 2. Pin Sharing Constraints by Subsystem

#### **NOTES:**

#1: The EMC and SDRAM interfaces share a number of pins, including address and data busses. While precluding exactly simultaneous accesses, careful attention to chip selects and controller programing allows them to be used within the same application, e.g. reading CompactFlash in IDE mode and writing SDRAM for HDD MP3 player applications. Recommendation: use driver level mutual exclusion semaphores.

#2: Within the EMC devices, conflicts can occur between shared pins in the NAND/SmartMedia interface and the CompactFlash interface. Use driver level mutual exclusion semaphores.

#3: Capless headphone mode common amplifier output shares a pin with the analog line 1 Right input. In addition, the headphone common mode sense input shares a pin with analog line 1 Left input. Only one of these uses can be designed into a specific application.

#### 2.5. Additional Documentation

Additional documentation and information is available from SigmaTel, including an extensive software development kit (SDK), application notes, reference schematics, sample PCB board layouts, sample bill of materials, etc.

It is specifically recommended that the reader refer to the peripheral device include files from the SDK. These files provide constant declarations for address offsets to the registers defined in the following sections. Note that the name of each programmable register defined in this data sheet corresponds to a C language #define or assembly language equate of the exact same name. In addition, these files contain

# D-Major™Audio System on Chip

declarations that allow symbolic access to the individual bit fields within these registers. User programs can include all of these peripheral include files by simply including the file hw\_equ.inc into their assembly files and hw\_equ.h into their C files.

#### 3. CHARACTERISTICS/SPECIFICATIONS

## 3.1. Absolute Maximum Ratings

| PARAMETER                                                                             | MIN            | MAX                  | UNITS |

|---------------------------------------------------------------------------------------|----------------|----------------------|-------|

| Ambient operating temperature (Note 1)                                                | -10            | 70                   | °C    |

| Storage temperature                                                                   | -40            | 125                  | °C    |

| Battery Pin (BATT) DCDCMODE 000, 001, 010,011                                         | -0.3           | 4.2                  | V     |

| Battery Pin (BATT) DCDCMODE 101,111                                                   | -0.3           | 1.98                 | V     |

| 5 Volt Source Pin (VDD5V)                                                             | -0.3           | 5.25                 | V     |

| PSWITCH DCDCMODE 101,111                                                              | -0.3           | BATT                 | V     |

| PSWITCH DCDCMODE 000,001,010,011 (Note 2).                                            | -0.3           | VddIO+0.6            | V     |

| Analog supply voltage (VddA1, 2, VddHP, VddPLL)                                       | Digital Supply | 1.98                 | V     |

| Digital supply voltage (VddD1, 2, 3)                                                  | -0.3           | Analog Supply        | V     |

| I/O Supply (VddIO1, 2, 3, 4)                                                          | -0.3           | 3.63                 | V     |

| DCDC converter #1 (DCDC_VddD)                                                         | -0.3           | VddD Rail            | V     |

| DCDC converter #1 (DCDC_VddA)                                                         | -0.3           | VddA Rail            | V     |

| DCDC converter #1 (DCDC_VddIO) DCDC Mode 000                                          | -0.3           | 4.2V                 | V     |

| DCDC converter #1 (DCDC_VddIO) all other DCDC Modes                                   | -0.3           | 3.6V                 | V     |

| DCDC converter #1 (DCDC_Batt)                                                         | -0.3           | max (VddIO,<br>BATT) | V     |

| DCDC converter #2 (DCDC2_Vout) DCDC Mode 000                                          | -0.3           | 4.2                  | V     |

| DCDC converter #2 (DCDC2_Vout) all other DCDC Modes                                   | -0.3           | 3.6                  | V     |

| Input voltage on any DCDC MODE input pin relative to ground (DCDCMOD) (Note 3)        | -0.3           | BATT                 | V     |

| Input voltage on any digital I/0 pin relative to ground (DIO3) (Note 3)               | -0.3           | VDDIO+0.3            | V     |

| Input voltage on any digital I/O pin in 1.8V mode relative to ground (DIO18) (Note 3) | -0.3           | VDDD+0.3             | V     |

| Input voltage on USB D+, D- pins relative to ground (USBIO) (Note 3)                  | -0.3           | 3.6                  | V     |

| Input voltage on any analog pin relative to ground (AIO) (Note 3)                     | -0.3           | VDDA+0.3             | V     |

#### **Table 3. Absolute Maximum Ratings**

#### Note:

- 1. Contact SigmaTel for extended temperature range options. In most systems designs, battery and display specifications will limit the operating range to well within these specifications.

- 2. The maximum voltage limit on the PSWITCH can be achieved in DCDCMODE 000, 001, 010, and 011 by tying the switch to VddIO through a  $10K\Omega$  resistor. The ESD protection diode limits the input voltage to an acceptable level. In mode 111 and mode 101, the switch is tied to the battery.

- 3. Pin sets for DCDCMODE, DIO3, DIO18, and AIO are defined in the pin list, see Table 489. "Pin Definition Table" on page 368.

# **Preliminary**

5-35xx-D1-1.03-091703 21

# D-Major™Audio System on Chip

## 3.2. Recommended Operating Conditions

| PARAMETER                                                  | MIN     | TYP  | MAX    | UNITS |

|------------------------------------------------------------|---------|------|--------|-------|

| Digital core supply voltage – VddD1, VddD2, VddD3 (Note 4) | 1.25    | -    | Analog | V     |

| Specification dependent on DSP frequency                   |         |      | Supply |       |

| Digital I/O supply voltage – VddIO1, VddIO2                | 2.9     | 3.0  | 3.6    | V     |

| Analog supply voltage – VddA(VddA1, VddA2, VddA3)          | Digital | -    | 1.98   | V     |

| Specification dependent on maximum output power            | Supply  |      |        |       |

| Battery startup input voltage in 1xAA or 1xAAA mode        | 0.9     | -    | -      | V     |

| Full Scale Input Voltage:                                  |         |      |        |       |

| Line Inputs (Note 5)                                       | -       | 0.6  | -      | Vrms  |

| Mic Input                                                  | -       |      | -      | Vrms  |

| With 20 dB boost                                           |         | 0.06 |        |       |

| Without 20 dB boost                                        |         | 0.6  |        |       |

| Full Scale Output Voltage with 16Ω load:                   |         |      |        |       |

| Headphone/Line Outputs (VddA = 1.8 V)                      | -       | 0.54 | -      | Vrms  |

| Headphone/Line Outputs (VddA = 1.35 V)                     | -       | 0.42 | -      | Vrms  |

| Crosstalk between input channels (16Ω loads at 1Khz)       | -       | -75  | -      | dB    |

| THD+N (16Ω headphone at 1 Khz)                             | -       | -70  | -66    | dB    |

| THD+N (10KΩ load at 1 Khz)                                 |         | -87  |        |       |

| Analog line input resistance (Note 6)                      | -       | 25   | -      | kΩ    |

| Microphone input resistance                                | -       | 100  | -      | kΩ    |

| Analog output resistance                                   | -       | -    | <1     | Ω     |

| DAC SNR Idle Channel (Note 7)                              | -       | 96   | -      | dB    |

| DAC -60dB dynamic range (Note 7)                           | 92      | 94   | -      | dB    |

| ADC SNR Idle Channel (Note 7)                              |         | 90   |        | dB    |

| ADC -60dB dynamic range (Note 7)                           |         | 90   |        | dB    |

| Line SNR (Note 7)                                          | 92      | 94   | -      | dB    |

| Standby Current (Note 8)                                   |         | TBD  | TBD    | uA    |

#### **Table 4. Recommended Operating Conditions**

Note: 4. Recommended operating voltages for DCLK can be found in Table 5.

- 5. At 1.35VddA max input is 0.45Vrms

- 6. Input resistance changes with volume setting:  $10K\Omega$  at +12dB,  $25K\Omega$  at 0dB,  $50K\Omega$  at -34.5dB

- 7. Measured "A weighted" over a 20 Hz to a 20 kHz bandwidth, relative to full scale output voltage (1.8V)

- 8. The chip consumes current when in the "OFF" mode to keep the crystal oscillator and the real time clock running. With a typical 2850mAh AA battery, the standby current would take more than 1 year to drain the battery fully. It also is possible to design a system that disables the crystal oscillator and real time clock to achieve a much lower OFF current.

# **Preliminary**

The following table can be used to select a proper setting for VddD and VddD brownout voltages based on standard analysis of worst case design and characterization data.

| MAX<br>DCLK<br>TARGET | Min.<br>VddD | HW_DCDC_VDDD_<br>VOLTAGE_LEVEL | Corresponding<br>VddD<br>Brownout Voltage | HW_DCDC_VDDD_<br>BROWNOUT_LEVEL |

|-----------------------|--------------|--------------------------------|-------------------------------------------|---------------------------------|

| 75MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 70MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 65MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 60MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 55MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 50MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 45MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 40MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 35MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 30MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 25MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 20MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 15MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 10MHz                 | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 5MHz                  | TBD V        | TBD                            | TBD V                                     | TBD                             |

| 200KHz                | TBD V        | TBD                            | TBD V                                     | TBD                             |

Table 5. Recommended Operating Conditions for specific dclk targets

After split lot characterization of the part performance versus speed sensor values, a closed loop method for setting VddD voltage and brownout levels will be provided which allows VddD settings to be tuned to the actual process corner of a part, at the then current ambient temperature and voltage.

# **Preliminary**

# D-Major™Audio System on Chip

# 3.3. DC Characteristics

| PARAMETER                                                                                                                                                         | MIN        | TYP | MAX      | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|----------|-------|

| Power Dissipation, VddD = TBD V, VddA = TBD V, VddIO = TBD V DCDC mode = TBD, DCLK = TBD MHz on PLL, USB off, Application = MP3 Play, minimum power configuration |            | TBD |          | mW    |

| selected.                                                                                                                                                         |            |     |          |       |

| $V_{iH}$ (DIO3) - Input high voltage for DIO3 digital I/O pin set, in 3.3 Volt mode.                                                                              | 2.0        |     |          | V     |

| $\rm V_{\rm IL}$ (DIO3) - Input low voltage for DIO3 digital I/O pin set in 3.3 Volt mode.                                                                        |            |     | 0.8      | V     |

| $V_{IH}$ (DIO18) - Input high voltage for DIO18 digital I/O pin set in 1.8 Volt mode.                                                                             | 0.7*VddD   |     |          | V     |

| V <sub>IL</sub> (DIO18) - Input low voltage for DIO18 digital I/O pin set in 1.8 Volt mode.                                                                       |            |     | 0.3*VddD | V     |

| V <sub>OH</sub> (DIO3) - Output high voltage for DIO3 digital I/O pin set in 3.3 Volt mode, 4mA mode.                                                             | 0.7VddIO   |     |          | V     |

| V <sub>OH</sub> (DIO3) - Output high voltage for DIO3 digital I/O pin set in 3.3 Volt mode, 8mA mode.                                                             | TBD        |     |          | V     |

| $V_{\rm OL}$ (DIO3) - Output low voltage for DIO3 digital I/O pin set in 3.3 Volt mode.                                                                           |            |     | 0.4      | V     |

| V <sub>OH</sub> (DIO18) - Output high voltage for DIO18 digital I/O pin set in 1.8 Volt mode.                                                                     | VddD - 0.4 |     |          | V     |

| $V_{\rm OL}$ (DIO18) - Output low voltage for DIO18 digital I/O pin set in 1.8 Volt mode.                                                                         |            |     | 0.4      | V     |

Table 6. DC Characteristics

# **Preliminary**

#### 4. DSP CORE

The on-chip DSP core is modeled exactly after the Motorola DSP56004. It supports the identical instruction set, registers, addressing modes, etc., as the DSP56000 family of digital signal processors. Figure 13 shows the DSP architecture. The DSP core is a general-purpose 24-bit DSP especially suited to high fidelity digital audio applications for very low power/energy environments.

Figure 13. DSP Architecture

5-35xx-D1-1.03-091703 25

# D-Major™Audio System on Chip

The central components are:

- Data Busses (XD,YD,PD)

- Address Busses (XA,YA,PA)

- Data Arithmetic Logic Unit (Data ALU)

- Address Generation Unit (AGU)

- Program Control Unit (PCU)

- · On-Chip Program ROM

- On-Chip X,Y,P RAM

- On-Chip Emulation circuitry

The DSP is organized around the registers of three independent execution units: the PCU, the AGU and the data ALU. Data movement between the execution units occurs over four bidirectional 24-bit busses: the X data bus (XDB), the Y data bus (YDB), the program data bus (PDB) and the global data bus (GDB). Certain instructions treat the X and Y data buses as one 48-bit data by concatenating them. Data transfers between the data ALU and the X data memory or Y data memory occur over the XDB and YDB respectively.

The bus structure supports general register-to-register, register-to-memory, and memory-to-register data movement. It can transfer up to two 24-bit words or one 56-bit word in the same instruction cycle.

Transfers between busses occur in the internal bus switch. The internal bus switch, which is similar to a switch matrix, can connect any two internal busses without adding pipeline delays. Thus greatly simplifying the programming model.

The bit manipulation unit is located in the bus switch so that it can access each memory space. The bit manipulation unit performs bit operations on memory locations, address registers, control registers and data registers over the XDB, YDB and GDB.

The data ALU performs all of the arithmetic and logical operations on data operands. It consists of four 24 bit input registers, two 48-bit accumulators and two 8-bit accumulator extension registers, an accumulator shifter, two data bus shifter/limiter circuits, and a parallel single cycle, non-pipelined multiply-accumulator (MAC) unit.

The address generation unit (AGU) performs all of the address storage and address generation computations necessary to indirectly address data operands in memory. It operates in parallel with other DSP resources to minimize address generation overhead and keep the supply of data operands fed to the data ALU. The AGU has two identical address arithmetic units that can generate two 16-bit addresses every instruction cycle. Each of the arithmetic units can perform one of three types of address arithmetic: linear, modulo and reverse-carry.

The program control unit performs instruction prefetch, instruction decode, hardware DO loop control, and interrupt/exception processing. It consists of three components: the program address generator, the program decode controller, and the program interrupt controller. It contains a 15-level by 32 bit system stack memory and the following directly addressable registers: the program counter (PC), loop address (LA), loop counter (LC), status register (SR), and the operating mode register (OMR).

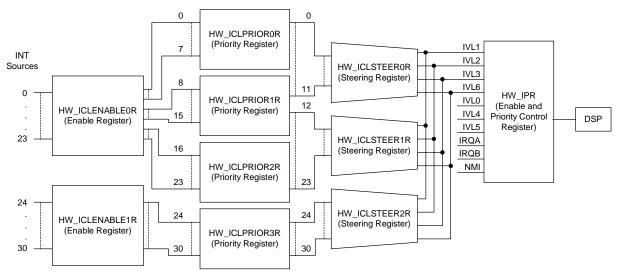

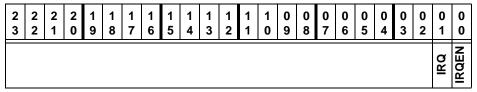

The DSP core responds to 7 interrupt vector level inputs (IVL[6:0], two peripheral interrupts (IRQA, IRQB) and a non-maskable interrupt (NMI).

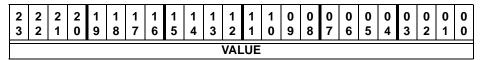

## 4.1. Operating Mode Register

The organization of the operating mode register is shown below. The operating mode register determines chip configuration including boot modes, and memory configuration. The HW\_OMR is a core register that is accessible by special DSP instructions. It therefore has no address.

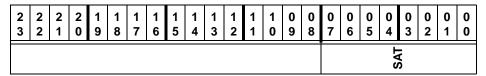

HW\_OMR

**SPECIAL**

| BITS | LABEL | RW | RESET | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23:8 | RSRVD | R  | 0     | Reserved – Must be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7    | MDLP  | RW | 0     | <b>Low Power Mode</b> – Writing a 0 to this bit enables some clock gating in the DSP core that reduces its power consumption. This register must be written with a 1 for proper operation of the debug functionality in the DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6    | SD    | RW | 0     | Stop Delay – This bit is exported from the core as an output. It can be used when waking up from the STOP low power standby mode. If this bit is set, then when an IRQA interrupt occurs to wake up the core from the STOP state, the clock control circuitry will wait a time period (e.g. 65536 clock cycles) before allowing the clocks back in to the DSP core. This can be used, for example, to restabilize a PLL clock oscillator. If this bit has a zero value, then the clocks will be allowed back into the core immediately after the occurrence of the IRQA interrupt, thus implementing a "warm boot" from the STOP low power standby state.                                                                                                                                             |

| 5    | RSRVD | R  | 0     | Reserved – Must be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4    | MC    | RW | GP0   | <b>Operating Mode C</b> – This bit is used to configure the boot mode for the STMP35xx. When the hardware reset is active, this bit samples the state of GP0 pin. Once the boot code executes, it can check the state of this bit in order to make decisions about what type of boot mode to perform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3    | YD    | RW | 0     | Internal Y-Memory Disable – This bit has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2    | DE    | RW | 1     | Data ROM Enable – This bit has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1    | МВ    | RW | GP1   | <b>Operating Mode B</b> – This bit is used to configure the boot mode for the STMP35xx. When the hardware reset is active, this bit samples the state of the GP1 pin. Once the boot code executes, it can check the state of this bit in order to make decisions about what type of boot mode to perform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

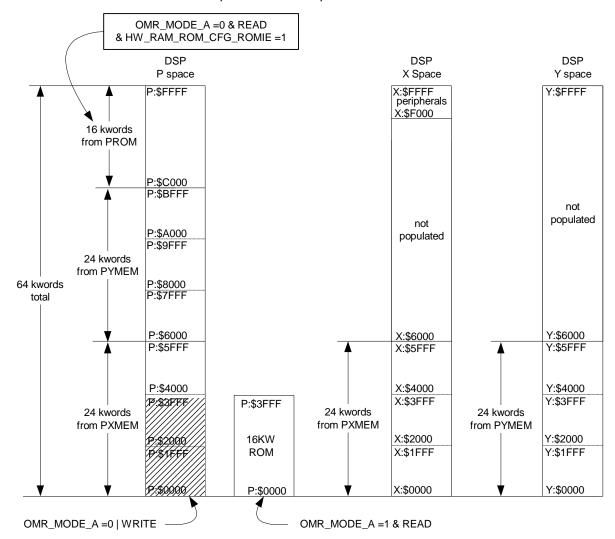

| 0    | МА    | RW | 1     | Operating Mode A – This bit is used to choose between Boot ROM and Program Memory for instruction fetches and read accesses. When this bit is set, as it is after hardware reset, the Boot ROM space is activated and any fetches or read accesses to the P: space will refer to the on-chip ROM. When this bit is a zero, the Program RAM Memory space is enabled instead of the Boot ROM memory space and any fetch or read access to P: space will refer to the on-chip RAM. Writes to P: space always access the program RAM regardless of the state of the MA bit. It is not possible to write to the program ROM. This bit affects ROM access in region P:\$0000 through P:\$3FFF. Accesses to the high mapped region of ROM, P:\$C000 through P:\$FFFF is controlled by HW_RAM_ROM_CFG_PROMIE. |

**Table 7. Operating Mode Register Description**

# 4.2. General Debug Register

The HW\_GDBR Register is also mapped into the X Peripheral I/O space. This register is used as a gateway between the DSP and the Debug port. For instance, when displaying the states of the internal registers and memory of the DSP core, the DSP moves the data to this register and the data is then shifted out the OnCE\_DSO pin. The HW\_GDBR register operation is controlled automatically by the emulator and the debug circuitry within the core. An added feature of the Debug Unit is that the

5-35xx-D1-1.03-091703 27

# D-Major™Audio System on Chip

emulator cannot access the debug unit unless a write to the HW\_GDBR Register is executed by the DSP (normally in the boot code).

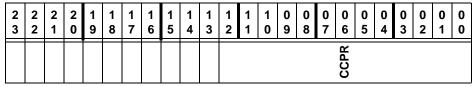

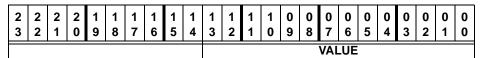

HW\_GDBR X:\$FFFC

Table 8. HW\_R

| BITS | LABEL | RW | RESET | DEFINITION                                                                                            |

|------|-------|----|-------|-------------------------------------------------------------------------------------------------------|

| 23:0 | VALUE | RW | 0     | Value to be read by the debugger or debugger value to be read by a DSP instruction from the debugger. |

Table 9. General Debug Register (GDBR)

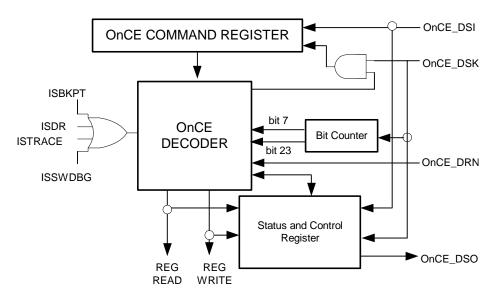

## 4.3. OnCE (On-Chip Emulator) Debug Interface

The DSP on-chip emulation (OnCE) circuitry provides a sophisticated debugging tool that allows simple, inexpensive, and speed independent access to the processor's internal registers, memories and peripherals. OnCE provides software engineers with access to the internal state including the addresses of the last five instructions and provides the ability to modify that state, and single step the processor. OnCE capabilities are accessed through a four pin interface

- 1. Debug Serial input (OnCE\_DSI)

- 2. Debug Serial Clock (OnCE\_DSK)

- 3. Debug Serial Output (OnCE\_DSO)

- 4. Debug Request Input (OnCE\_DRN)

The OnCE controller and serial interface consists of the following blocks: OnCE command register, bit counter, OnCE decoder and the status/control register. For a block diagram, see Figure 14. "OnCE Interface Block Diagram" on page 29.

Figure 14. OnCE Interface Block Diagram

The OnCE Command Register is an 8 bit shift register that receives the serial data from the OnCE\_DSI pin. It holds the 8 bit commands to be used as input for the OnCE controller.

| OnCE ( | Command | Rec | iister |

|--------|---------|-----|--------|

|--------|---------|-----|--------|

| BITS | LABEL | RW | RESET | DEFINITION                                                                                                                                                                                                                                                                                                |

|------|-------|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | RW    | RW |       | The read/write bit specifies the direction of the data transfer. For zero, write the data associated with the command into the register specified in the <b>RS</b> field. For one, read the data contained in the register specified in the <b>RS</b> field.                                              |

| 6    | GO    | RW |       | If the GO bit is set, the chip will execute the instruction which resides in the PIL register. To execute the instruction, the processor leaves the debug mode, and the status is reflected on the OS0,OS1 pins. The processor will return to the debug mode immediately after executing the instruction. |

| 5    | EX    | RW |       | If the Exit Command bit is set, the processor will leave the debug mode and resume normal operation. The Exit command is executed only if the Go command was issued and the operation is a write to OPDBR or a read/write to" No Register Selected".                                                      |

| 4:0  | RS    | RW |       | Register Select field                                                                                                                                                                                                                                                                                     |

Table 10. OnCE Command Register

The Register Select field (RS[4:0]) selects one of 32 OnCE debug registers to be read or written.

| RS[4:0] | REGISTER SELECTED                |  |  |  |  |  |

|---------|----------------------------------|--|--|--|--|--|

| 00000   | OnCE Status and Control Register |  |  |  |  |  |

| 00001   | Memory Breakpoint register       |  |  |  |  |  |

| 00010   | Reserved                         |  |  |  |  |  |

| 00011   | Trace Counter                    |  |  |  |  |  |

| 0010X   | Reserved                         |  |  |  |  |  |

| 00110   | Memory Upper Limit               |  |  |  |  |  |

| 00111   | Memory Lower Limit               |  |  |  |  |  |

**Table 11. OnCE Register Selects**

# D-Major™Audio System on Chip

| RS[4:0] | REGISTER SELECTED                                                               |

|---------|---------------------------------------------------------------------------------|

| 01000   | GDB Register NOTE: this register can be read or written by the DSP instructions |

| 01001   | PDB Register                                                                    |

| 01010   | PAB Register for Fetch                                                          |

| 01011   | PIL register, next instruction from debugger comes from here                    |

| 01100   | Clear Memory Breakpoint Counter                                                 |

| 01101   | Reserved                                                                        |

| 01110   | Clear Trace Counter                                                             |

| 01111   | Reserved                                                                        |

| 10000   | Reserved                                                                        |

| 10001   | Program Address Bus FIFO and Increment Counter                                  |

| 10010   | Reserved                                                                        |

| 10011   | PAB Register for Decode                                                         |

| 101XX   | Reserved                                                                        |

| 11XX0   | Reserved                                                                        |

| 11111   | No Register Selected                                                            |

Table 11. OnCE Register Selects

# D-Major™Audio System on Chip

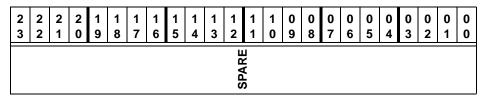

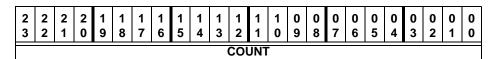

#### 5. ON-CHIP MEMORY SUBSYSTEM

The chip includes 96 kwords of on-chip RAM (96k x 24 bits = 2.25 Mbits) that is used for program and data storage, and 16K words of on-chip ROM (16K x 24 bits = 384kbits) that is used for the code that boots the device (see Section 20 for more details on boot modes and the contents of the on-chip ROM). The on-chip ROM is mapped at the address range P:\$0000-\$3FFF at reset, it can also be configured to be mapped at address range P:\$CFFF-\$FFFF, or it can be disabled.

The on-chip RAM is organized into two banks of 48K words each, called PXRAM and PYRAM. PXRAM can be mapped into the DSP P memory space, starting at P:\$0000, or into the DSP X memory space, starting at X:\$0000. PYRAM can be mapped into the DSP P memory space, starting immediately after the end of the PXRAM memory, or into the DSP Y memory space, starting at Y:\$0000. Both PXRAM and PYRAM memory can be allocated to the DSP P, X or Y memory spaces in 8K word increments, from a minimum of 0K words to all available memory. The memory configuration is controlled by the PX & PY Memory Configuration registers documented below. There are no hardware safeguards against improper programming of these registers. It is possible to allocate less than all of the on-chip RAM, unallocated memory will then be invisible to the DSP.

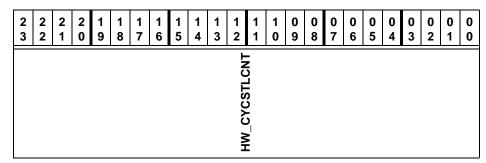

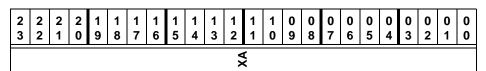

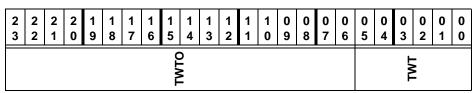

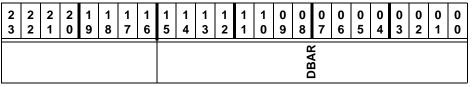

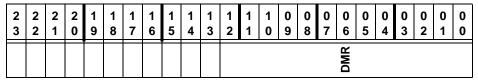

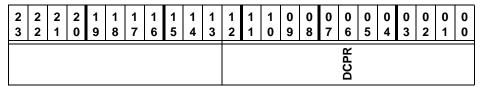

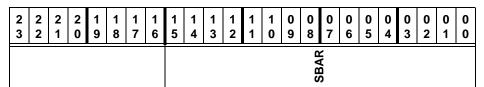

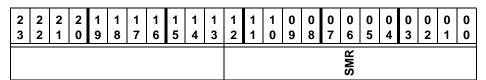

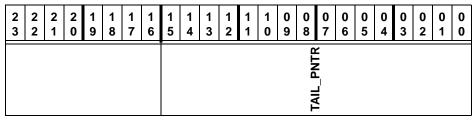

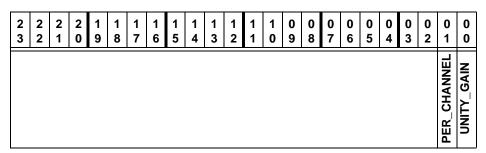

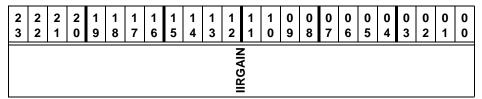

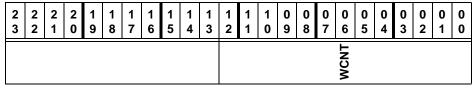

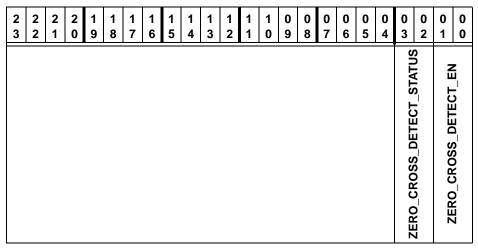

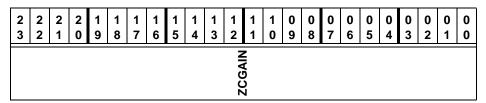

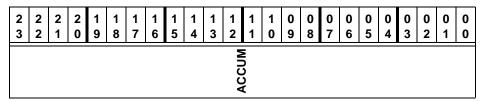

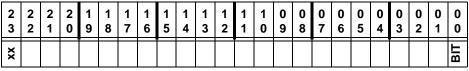

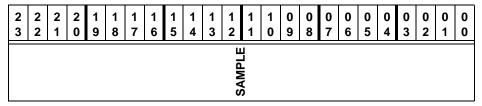

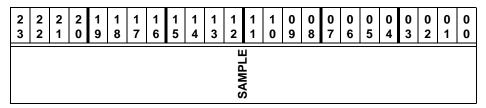

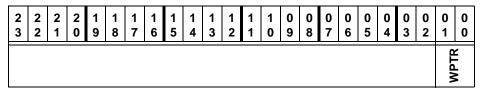

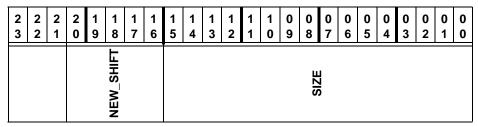

## 5.1. PXRAM Configuration Register

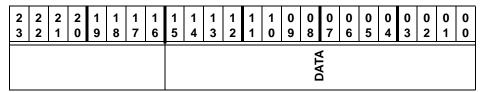

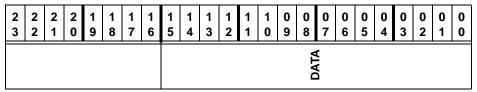

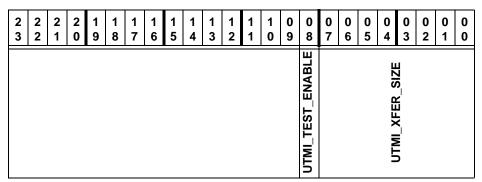

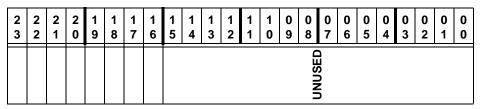

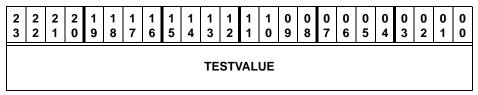

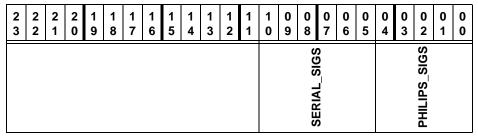

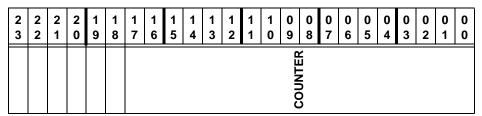

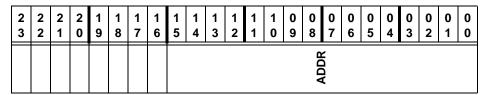

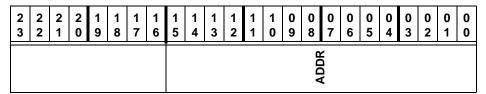

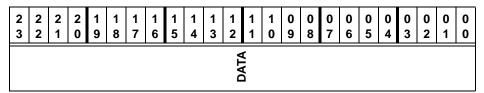

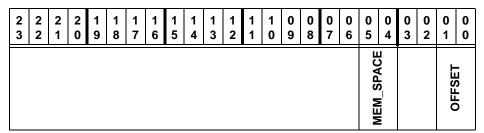

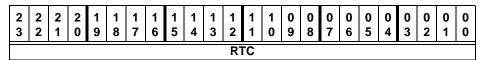

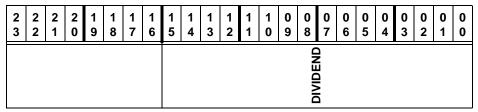

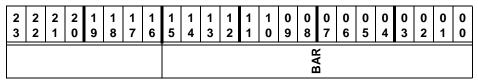

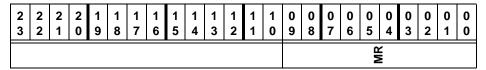

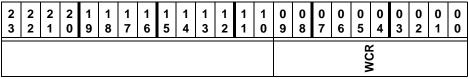

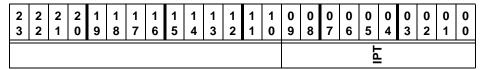

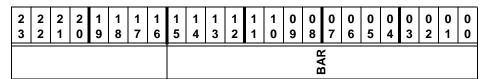

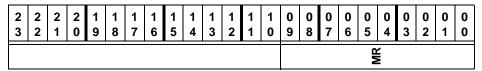

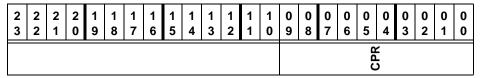

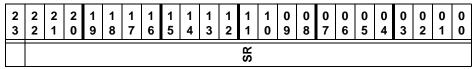

HW PXCFG X:\$FFE8

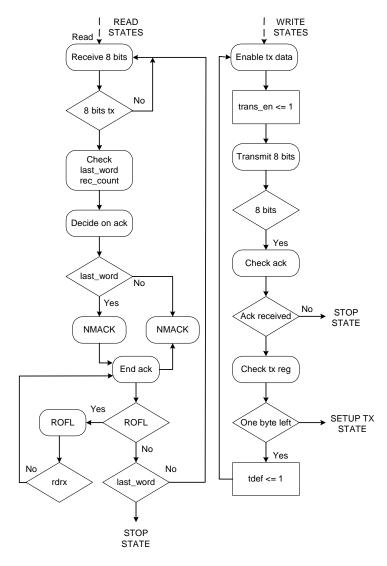

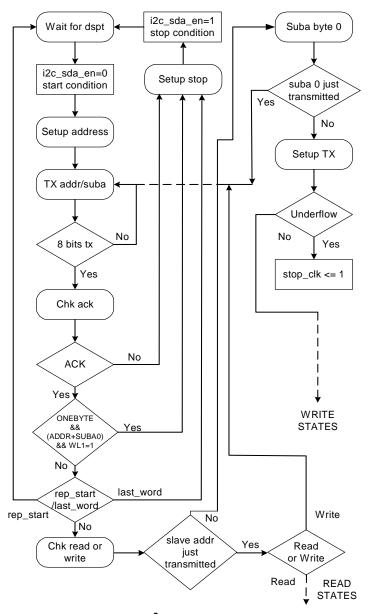

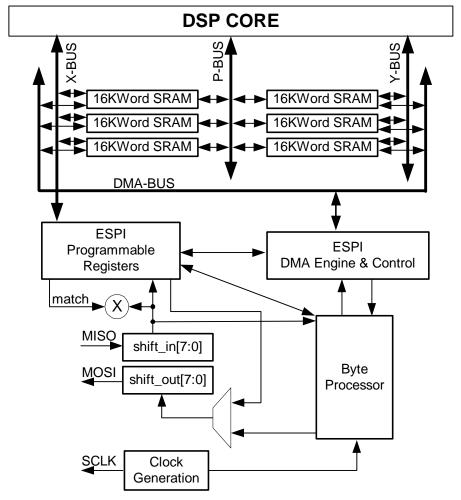

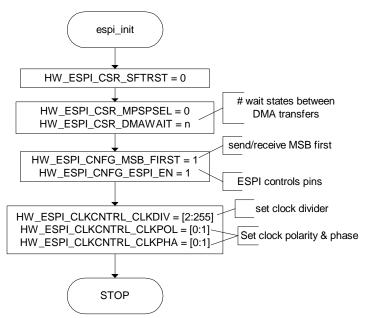

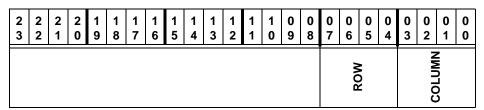

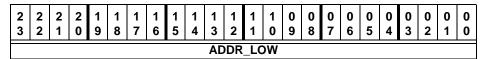

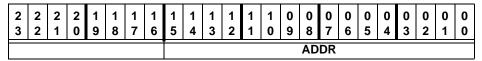

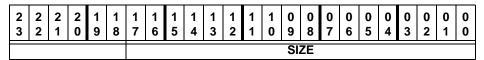

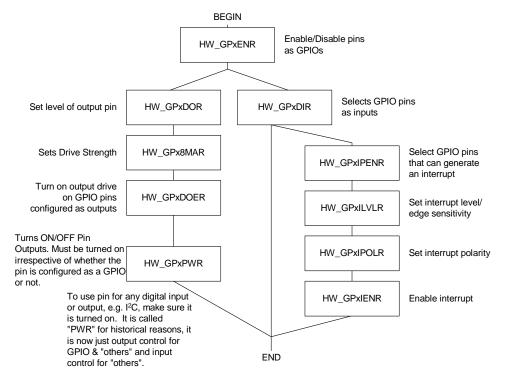

| 2 | 2 2 | 2 | 2 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1 | 1 2 | 1       | 1<br>0  | 0<br>9 | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | 0<br>4 | 0<br>3  | 0<br>2 | 0<br>1 | 0 |